Table of Contents

21 Apr 2026 — Nature Reviews Electrical Engineering published a comprehensive review titled “CMOS compatibility of semiconductor spin qubits” (Dumoulin Stuyck, Saraiva, Gilbert, Cifuentes Pardo, Li, Escott, De Greve, Voinigescu, Reilly & Dzurak), systematically evaluating where silicon spin qubits align with established semiconductor manufacturing and where they diverge from it. The paper originated as a pre-print on arXiv (arXiv:2409.03993) in September 2024; the final peer-reviewed version appeared on April 20, 2026 – substantially updated with references to key 2025 results that postdate the original submission.

The authors span UNSW Sydney, Diraq, imec, the University of Toronto, and the University of Sydney (Emergence Quantum). It is worth noting the competing interests: six of the ten authors hold equity in Diraq, and Andrew Dzurak is Diraq’s CEO. This does not diminish the technical content — these are among the world’s foremost silicon spin qubit researchers — but it frames the review as an advocacy document as much as a neutral survey.

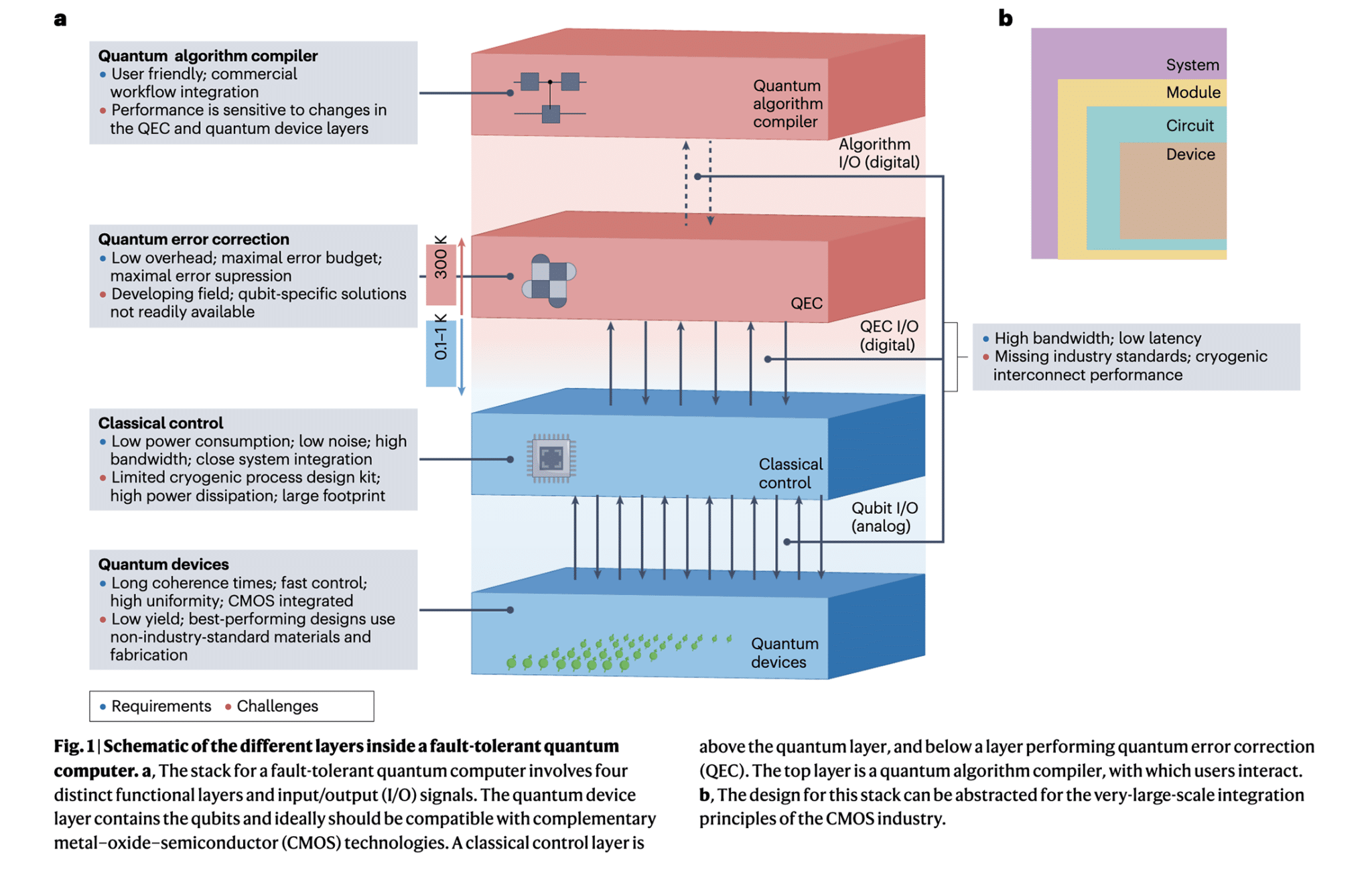

The review arrives at a moment when silicon’s credibility as a quantum computing platform has surged. In September 2025, a companion paper from largely the same team (Steinacker, Dumoulin Stuyck, Dzurak et al.) demonstrated >99% fidelity across all operations in silicon spin qubits fabricated at imec’s 300 mm foundry. That result showed the performance was achievable in a manufacturing environment. This review asks the harder question: what does it actually take to get from a few working qubits on a 300 mm wafer to a fault-tolerant processor with millions of them?

The bottom line: silicon spin qubits are not just “CMOS-compatible” in the marketing sense of being fabricated on silicon wafers. They are structurally aligned with CMOS very-large-scale integration (VLSI) principles in ways that other qubit modalities are not — but significant engineering gaps remain, particularly in materials, cryogenic operation, and the co-integration of qubits with their classical control electronics.

What the Review Covers

The review is structured around the overlap, and the gaps, between spin qubit requirements and standard CMOS industry practices. Several elements stand out.

The Economics Argument

The review opens with a framing that quantum computing discussions too often skip: cost. The authors define utility scale as the point where a quantum computer’s economic value exceeds its cost, and they put a sharp number on the energy dimension. They cite an estimate that a superconducting quantum computer would need 38 GJ of energy to crack the most widely used cryptographic key in 1.5 hours — comparable to a car burning 20 full tanks of petrol. And that’s a single algorithm execution. Quantum chemistry applications, where near-term commercial value is more likely, might require thousands of such calculations.

This is a useful reality check. Quantum computing’s economic viability depends not just on whether something can be computed, but whether it can be computed at a price that justifies the infrastructure. The authors argue that CMOS-native fabrication, with its decades of cost optimization through scaling, is the only realistic path to bringing those costs down.

Degrees of CMOS Compatibility

The authors make a critical distinction that is often lost in quantum computing marketing. “CMOS compatible” can mean anything from fabricating a qubit on a silicon wafer (a minimal claim) to fully co-integrating millions of qubits with the classical control electronics needed to operate them on the same chip (the actual goal). The review identifies a spectrum of compatibility and argues that semiconductor spin qubits sit at the deep end of this spectrum, because the architecture inherently supports it.

Spin qubits are electrostatically defined quantum dots with submicrometre footprints and planar gate layouts. That description could apply equally to a modern transistor. Other qubit modalities can be fabricated using some CMOS tools, but their operational requirements are fundamentally different from what CMOS fabs are designed to produce. The review notes that photonic qubits now use silicon waveguides, superconducting qubits have moved from sapphire to silicon substrates, and trapped ions use microfabricated electrode grids — but these are retrofits, not native compatibility.

The Scaling Argument

The review presents a spin qubit roadmap (Fig. 2) estimating that academic cleanroom fabrication hits a practical ceiling due to yield limitations, while foundry fabrication opens the path to the millions of qubits required for fault-tolerant algorithms. The roadmap sketches three technology regimes: room-temperature control, system-in-package, and system-on-chip; with increasing qubit counts at each stage.

A striking claim: millions of qubits can feasibly fit on a single chip, assuming a chip area of 10 mm² and an average qubit size of 100 nm². The authors note that spin qubits are the only technology that can achieve fault tolerance without resorting to a modular approach — no coherent quantum links between separate modules, no entanglement distillation overhead, no inter-module error budget. This is a direct competitive argument against superconducting and trapped-ion architectures, which rely on modular scaling.

The review also notes that QEC-compatible entanglement has not yet been demonstrated for modular coupling in any qubit system. And that near-term value for noisy intermediate-scale quantum (NISQ) algorithms has not been found as of 2026, confirming that the path to useful quantum computing runs through fault tolerance and millions of qubits, not through NISQ shortcuts.

Where the Gaps Are

The review is notably honest about the divergences. Three stand out:

Millikelvin operation. Standard CMOS operates at room temperature or, for some specialized applications, at cryogenic temperatures around 4 K. Spin qubits currently achieve their highest fidelities at tens of millikelvin — three orders of magnitude colder. The review discusses “hot qubit” demonstrations above 1 K (Yang et al. 2020, Petit et al. 2020, Huang et al. 2024) as a potential pathway to relaxing this requirement, but acknowledges that high-temperature operation currently comes with reduced fidelity. The cryogenic gap is not just an engineering inconvenience; it determines how much classical electronics can be co-located with the qubits, which in turn determines the feasibility of the wiring density needed for millions of qubits.

The power budget numbers are sobering. Commercially available pulse tube cryostats offer 2–4 W of cooling power at 4 K, setting an upper bound of less than 4 µW per qubit for control electronics in a million-qubit processor. Current cryo-CMOS demonstrations (Fig. 4b in the paper) show power consumption per qubit roughly 1,000-fold too high when extrapolated to a million qubits and compared to the cooling power of commercially available systems compatible with spin qubits — around 100 mW at millikelvin temperatures. The review flags the recent cryo-CMOS control chip operating at millikelvin temperatures (Bartee et al. 2025) as a key milestone, but the gap remains formidable.

Materials. CMOS foundries use high-κ dielectrics (like HfO₂) for gate oxides because they enable continued transistor scaling. Spin qubits, however, are exquisitely sensitive to charge noise, and high-κ dielectrics are noisier than the thermal SiO₂ used in older process nodes. The review discusses isotopic purification of silicon-28 (to eliminate magnetic noise from silicon-29 nuclear spins) and the tension between the materials that make good transistors and the materials that make good qubits. Deposition of ²⁸Si on 300 mm wafers has been demonstrated at 99.992% purity – but this is not yet offered commercially. Valley splitting – an energy parameter critical for spin qubit operation that depends sensitively on the atomic-scale details of the Si/SiO₂ or Si/SiGe interface – adds another materials constraint without a direct CMOS analog.

Design rules and variability. CMOS manufacturing manages transistor variability through statistical design rules – billions of transistors don’t all need to be identical, just within specification. Spin qubits have much tighter tolerances. The review explores how device variability propagates into qubit performance and discusses three approaches to managing it: uniform qubits with shared control (using crossbar addressing, Li et al. 2018), variable qubits with individual control (system-on-chip integration), and variable qubits with robust control (pulse engineering techniques like the SMART protocol). The first approach reduces I/O line scaling to roughly the square root of qubit count — a significant improvement, though still demanding.

Architecture and Volume Testing

The review covers scaling architectures including the crossbar network (Li et al. 2018), which uses shared control lines to reduce wiring density, and the spiderweb array (Boter et al. 2022), which arranges qubits in a sparse lattice optimized for surface code error correction. Both architectures are designed to work within CMOS wiring constraints, but neither has been demonstrated at scale.

One area where the published version adds significant detail is volume testing. The review describes the development of cryogenic probe stations operating at ~1.6 K for 300 mm wafers, enabling performance measurements of thousands of devices per day – several orders of magnitude faster than individual device measurements in dilution refrigerators. Intel has demonstrated single-electron probing across entire 300 mm wafers (Neyens et al. 2024). Thomas et al. (2025) achieved rapid cryogenic characterization of 1,024 integrated silicon quantum dot devices. And Tosato et al. (2026) recently published a crossbar chip specifically designed for benchmarking semiconductor spin qubits at volume — a tool that didn’t exist two years ago.

The gate pitch convergence data is striking (Fig. 4a). The contacted gate pitch of commercial CMOS nodes has been dropping steadily – 3 nm FinFETs now achieve 45 nm pitch. SiMOS spin qubits need gate pitches below 50 nm for fault-tolerance-compatible two-qubit gates. Those two curves are converging. The original 1999 proposal for a coupled SiMOS quantum gate assumed 15 nm pitch, far beyond what was commercially available then, but increasingly within reach of advanced lithography.

The Control Electronics Bottleneck

The control electronics discussion is particularly important for anyone tracking the path to a cryptographically relevant quantum computer (CRQC). A CRQC running Shor’s algorithm requires not just millions of physical qubits but the ability to execute deep circuits continuously for hours or days — the capability I track as D.3: Continuous Operation in my CRQC Quantum Capability Framework. Co-integrating classical control at millikelvin temperatures is essential for this; routing millions of control lines from room temperature to a dilution refrigerator is a physical impossibility.

The review identifies four possible levels of electronics integration, from minor circuits interspersed between qubits, through system-on-chip, to system-in-package, to cabled connections at separate temperature stages. All four levels could be required simultaneously depending on the component. The absence of open cryo-CMOS process design kits is flagged as a specific bottleneck holding back power-optimized designs.

My Analysis: What This Means for Silicon’s Position

The Strongest Case Yet for Silicon’s Structural Advantage

I wrote in March that silicon is the dark horse of quantum computing – the platform that has quietly assembled every building block for fault-tolerant quantum computing while the headlines went to superconducting processors and neutral atoms. This review strengthens that case substantially, but in a way that deserves precision rather than hype.

What makes this review significant is not a single experimental result but the systematic mapping of an integration pathway. Most quantum computing modalities have demonstrated individual capabilities such as high-fidelity gates, error correction, logical operations. But silicon is the only platform where someone has sat down and mapped, component by component, how the full stack from physical qubit to fault-tolerant processor aligns with an existing trillion-dollar manufacturing ecosystem.

That mapping reveals something important: the alignment is not superficial. Spin qubits are not just “made of silicon” the way a superconducting qubit might be fabricated on a silicon substrate. The gate structures, the electrostatic control, the planar layouts, the submicrometre feature sizes all overlap with CMOS design principles at a structural level. The review makes the case that for other modalities, CMOS compatibility is a retrofit; for spin qubits, it is inherent.

But Manufacturing Compatibility Is Not Manufacturing Readiness

The review is honest enough to serve as its own best counterargument. Three issues stand out as genuinely unsolved:

First, the materials gap is real. Isotopically purified silicon-28 is not a standard CMOS material. The 99.992% ²⁸Si epilayers demonstrated on 300 mm wafers are a specialized process not commercially offered. The question is whether foundries will invest in adding this capability – which creates a chicken-and-egg problem between demand and supply.

Second, the cryo-CMOS power gap is the most quantified unsolved problem in the paper. The 1,000-fold gap between current cryo-CMOS power consumption per qubit and what dilution refrigerator cooling budgets allow is not a rounding error. The Bartee et al. cryo-CMOS control chip is a genuine milestone – it demonstrated that cryo-CMOS circuits can control spin qubits at millikelvin temperatures without degrading two-qubit gate performance, but the power density challenge at scale remains open.

Third, device variability at scale remains the great unknown. The Steinacker et al. results showing consistent >99% fidelity across four randomly selected devices are encouraging — but four devices on a wafer is not four million. The review discusses automated tuning, machine-learning calibration, and the new rapid characterization tools (1,024 devices at cryogenic temperatures) as potential solutions, but these have not been demonstrated at the scale required. The review is candid that there is still no exact correlation between CMOS transistor yield and spin qubit yield.

Implications for CRQC Timelines

From a CRQC perspective, this review is relevant to at least three capabilities in my CRQC Quantum Capability Framework:

E.1: Engineering Scale & Manufacturability. This is where silicon’s advantage is most concrete. No other qubit modality has a comparably detailed public assessment of its manufacturability using existing industrial infrastructure. The review does not claim the problems are solved, but it establishes that the problems are tractable within an existing engineering framework; which is a meaningfully different statement than “we’ll figure out manufacturing later.”

B.3: Below-Threshold Operation & Scaling. The >99% fidelities demonstrated in foundry-fabricated devices place silicon spin qubits above the surface code threshold. The review’s discussion of biased noise (dominated by dephasing rather than bit-flip errors) suggests that tailored error correction codes, like the XZZX surface code, could further reduce overhead, a point I explored in the dark horse article.

D.3: Continuous Operation. The review’s discussion of cryo-CMOS co-integration directly addresses the wiring bottleneck that currently limits continuous operation of large quantum processors. If control electronics can be co-located at millikelvin or 1 K temperatures, the path to sustained multi-hour computations (thnk CRQC) becomes architecturally feasible.

The Missing Milestone and the Data Centre Vision

The review’s outlook section identifies a concrete next milestone for the field: the demonstration of quantum error correction using semiconductor spin qubits and specifically, achieving logical qubits with logical error rates lower than the corresponding physical error rate. This benchmark has been achieved by superconducting qubits (Google, 2024) and neutral atoms (Harvard-MIT-QuEra, 2024), but not yet by silicon. Until silicon crosses this threshold, the scalability argument remains theoretical.

The outlook also frames data-centre integration not just as a deployment detail but as a design driver. Embedding quantum processors within a CMOS-native data centre ecosystem and leveraging decades of innovation in reliability, scalability, monitoring, and fault recovery, could define operational protocols that reinforce silicon’s advantages. This is a vision that competes directly with the standalone-cryostat model that dominates current quantum computing architectures.

The Bigger Picture

The timing of this publication is worth noting. The pre-print appeared in September 2024, when silicon spin qubits were still widely viewed as a promising but distant contender. The peer-reviewed version appears in April 2026, substantially updated with references to the foundry-fabricated >99% fidelity result (Steinacker et al. 2025), the cryo-CMOS control at millikelvin temperatures (Bartee et al. 2025), Google’s below-threshold surface code result (Acharya et al. 2025), and other developments that postdate the original submission. This is a review that was written in one era and published in another — and the field moved in its direction during the interim.

This review is best read as a roadmap document. It does not claim silicon spin qubits are ready for production. It claims, with considerable technical detail, that the path from laboratory demonstrations to industrial-scale fault-tolerant processors is shorter for silicon spin qubits than for any other modality, because that path runs through infrastructure that already exists.

Quantum Upside & Quantum Risk - Handled

My company - Applied Quantum - helps governments, enterprises, and investors prepare for both the upside and the risk of quantum technologies. We deliver concise board and investor briefings; demystify quantum computing, sensing, and communications; craft national and corporate strategies to capture advantage; and turn plans into delivery. We help you mitigate the quantum risk by executing crypto‑inventory, crypto‑agility implementation, PQC migration, and broader defenses against the quantum threat. We run vendor due diligence, proof‑of‑value pilots, standards and policy alignment, workforce training, and procurement support, then oversee implementation across your organization. Contact me if you want help.