Silicon Crosses the Logical Threshold: First Universal Logical Operations Demonstrated in a Silicon Quantum Processor

Table of Contents

24 Mar 2026 – In 1998, Bruce Kane published a single-page proposal in Nature that launched an entire subfield of quantum computing. The idea was elegant: use the nuclear spins of individual phosphorus atoms embedded in a silicon crystal as qubits. Silicon offered long coherence times. Phosphorus offered an addressable spin. And the surrounding semiconductor infrastructure — the lithography, the fabrication processes, the supply chains that already produced billions of transistors — offered something no other quantum platform could: a plausible path to mass manufacturing.

Twenty-eight years later, Kane’s vision has reached a milestone that silicon’s competitors achieved first but that silicon may ultimately exploit most effectively. A team at the Shenzhen International Quantum Academy (SZIQA) and Southern University of Science and Technology (SUSTech), led by Dapeng Yu and Yu He, has demonstrated universal logical gate operations in a silicon quantum processor for the first time. Published in Nature Nanotechnology, the work uses five phosphorus nuclear spins embedded in an isotopically purified silicon lattice to encode two logical qubits, execute a complete universal gate set including the critical non-Clifford T gate, and run a variational quantum eigensolver algorithm on encoded logical qubits — computing the ground-state energy of a water molecule.

It is the first time any silicon platform has operated at the logical level. And it comes from China.

What the Experiment Actually Achieved

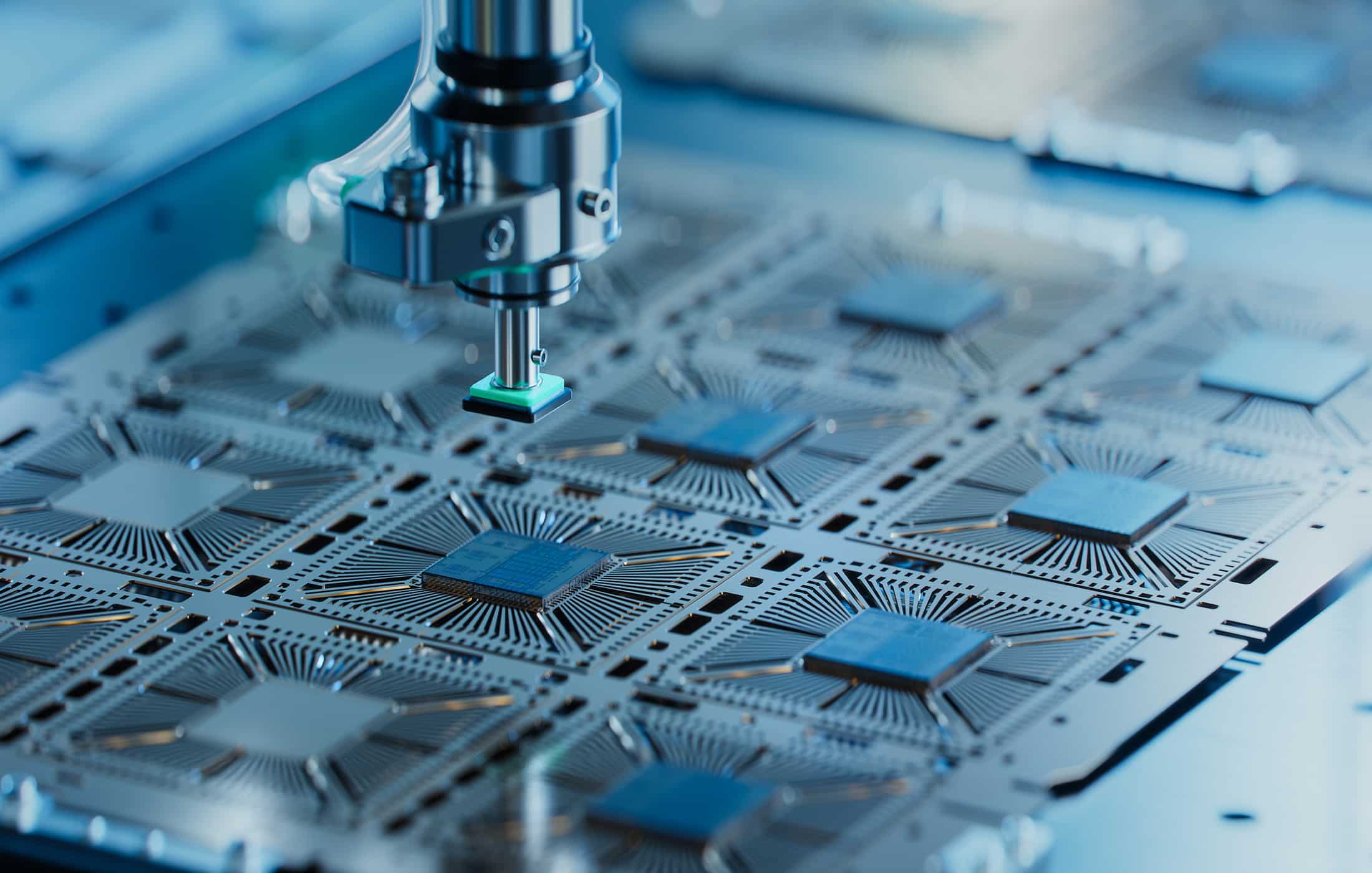

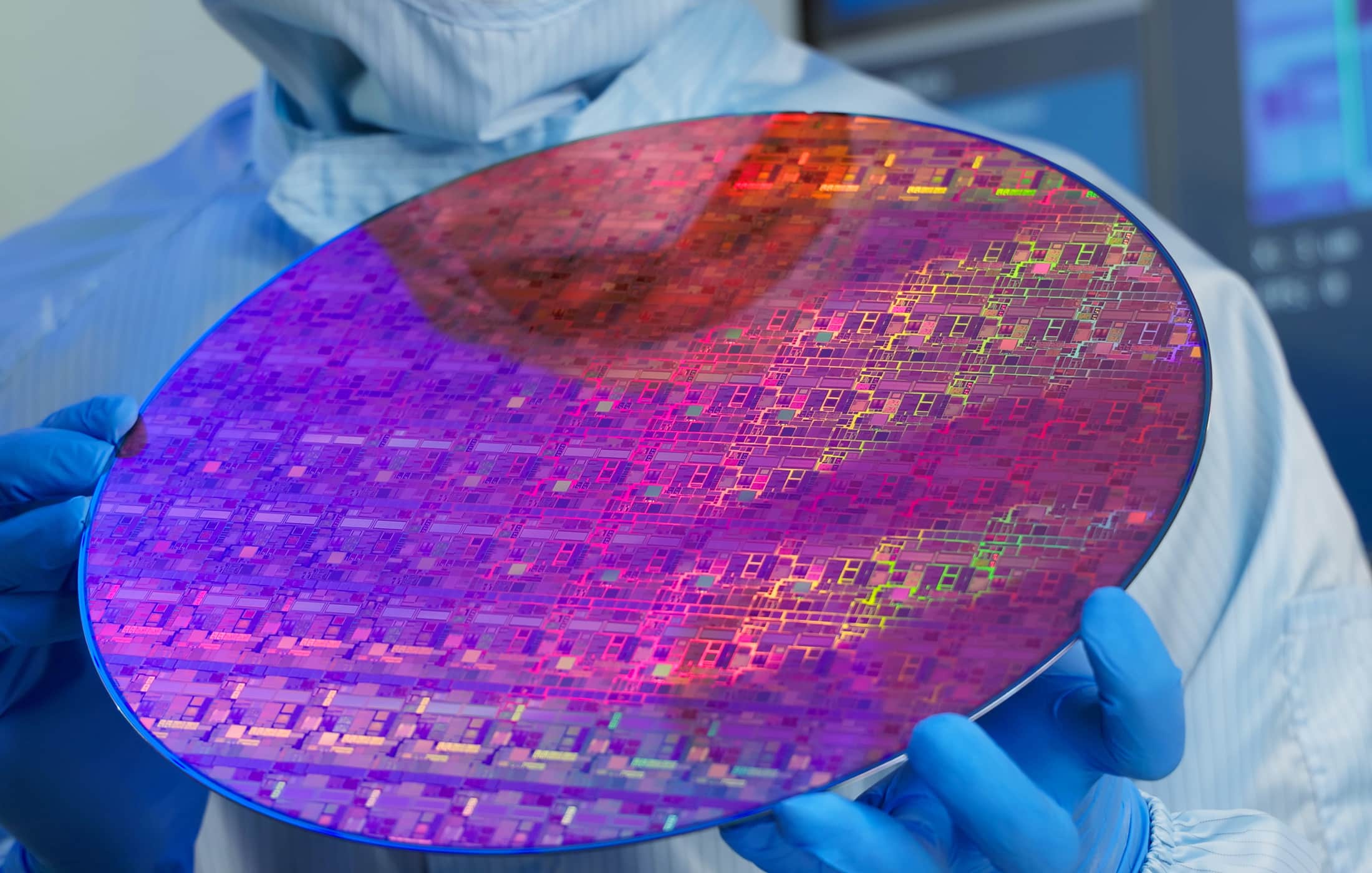

The researchers fabricated their device using scanning tunnelling microscopy (STM) lithography — the same technique pioneered by Michelle Simmons’ group at UNSW, now commercialized through Silicon Quantum Computing (SQC). STM lithography allows individual phosphorus atoms to be placed into a silicon crystal with atomic precision. The working processor consists of a single donor cluster: five phosphorus atoms sharing one electron, embedded between layers of isotopically purified ²⁸Si (with ²⁹Si concentration below 130 parts per million, minimizing the nuclear spin noise that remains the primary decoherence source in silicon qubits).

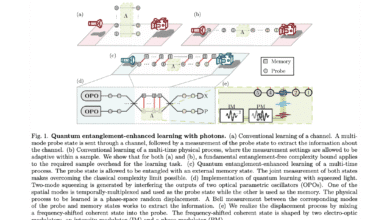

The five nuclear spins of those phosphorus atoms serve as qubits. The single shared electron mediates multi-qubit interactions through hyperfine coupling, enabling a native gate set that includes high-connectivity CCCCZ-type gates — effectively multi-controlled-Z operations that would require significant decomposition on other architectures. Single-qubit control is achieved through nuclear magnetic resonance (NMR) pulses, while the multi-qubit gates exploit electron spin resonance (ESR) transitions conditioned on specific nuclear spin configurations. This is the same physical mechanism — electron-mediated coupling between donor nuclear spins — that underpins the donor qubit approach across all groups working in this space.

Using this native gate set, the team implemented the [[4, 2, 2]] quantum error-detecting code — a code highlighted by Daniel Gottesman specifically for its minimal resource requirements in demonstrating fault tolerance. The code encodes two logical qubits across four physical qubits, with the fifth serving as an ancilla for the T gate implementation.

The key results, stated precisely:

The logical state |00⟩_L was prepared with a raw physical fidelity of 84.2%, improving to 96.5% after stabilizer parity postprocessing. The logical Bell state |Φ⁺⟩_L achieved 80.5% raw fidelity, rising to 95.5% after postprocessing — representing more than a four-fold reduction in error. Acceptance ratios remained above 82%, meaning the error detection discarded less than one in five measurements.

The team then demonstrated the complete universal gate set. The fault-tolerant logical gates X_L, CNOT_L, and H_L⊗H_L achieved population transfer fidelities of 88.3%, 88.6%, and 75.6% respectively. The non-fault-tolerant S_L gate reached 87.0% process fidelity via quantum process tomography. Critically, the logical T gate — the non-Clifford gate without which computation remains classically simulable per the Gottesman-Knill theorem — was implemented using the gate-by-measurement method, achieving 82.6% process fidelity.

These are not numbers that would support fault-tolerant computation at scale. The researchers are clear-eyed about this. But that misses the point: the demonstration is a proof of architecture, not a claim of operational readiness. No silicon platform had previously operated at the logical level at all.

Why the T Gate Matters More Than You Think

For readers tracking quantum error correction across platforms, the logical Clifford gates (X, S, H, CNOT) are necessary but not sufficient for universal quantum computation. The T gate completes the universal set, and it is notoriously difficult to implement fault-tolerantly — typically requiring a supply of “magic states” that must be prepared and then distilled to achieve sufficient fidelity.

The SZIQA team’s demonstration of the T gate through gate-by-measurement is significant for two reasons. First, it shows the technique works in silicon, using nuclear spin measurements to inject non-Clifford rotations onto logical qubits. Second, the magic states produced by the T gate circuit achieved fidelities as high as 95.2% — exceeding the 92.7% distillation threshold for H-type magic states established by Bravyi and Kitaev. This means at least one of the experimentally prepared magic states is already distillable, which is the gateway to fault-tolerant universal computation through adaptive magic-state distillation protocols.

The magic state result is arguably the most forward-looking finding in the paper. Magic state distillation remains one of the primary resource bottlenecks in fault-tolerant quantum computing architectures — as the Pinnacle Architecture analysis and resource estimation literature have quantified, the rate of magic state production directly determines both the physical qubit overhead and the wall-clock runtime of fault-tolerant computations. Demonstrating distillable magic states in silicon, even at this small scale, confirms that the platform’s fundamental physics supports the most resource-intensive component of fault-tolerant computation.

The Biased Noise Advantage

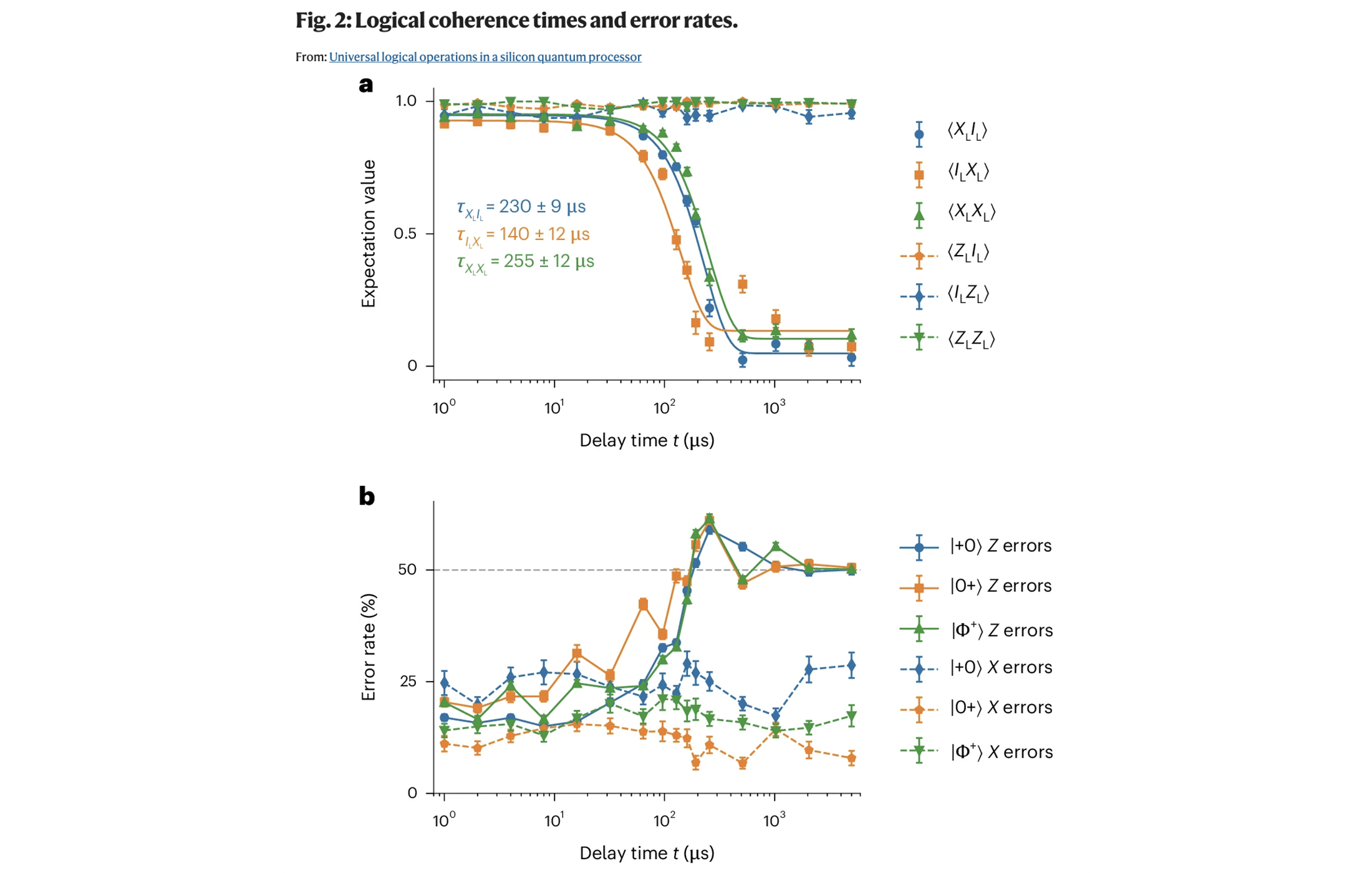

A finding that may prove more consequential than any single fidelity number is the team’s characterization of the noise profile in their system. Their measurements revealed strongly biased noise: phase-flip (Z) errors dominate overwhelmingly over bit-flip (X) errors. The bit-flip error rate remained essentially flat throughout the measurement period, while phase-flip errors grew as qubits decohered — reflecting the fact that nuclear spins in silicon have extremely long lifetimes (the Z-basis observables showed no detectable decay during the entire measurement window) but finite coherence times.

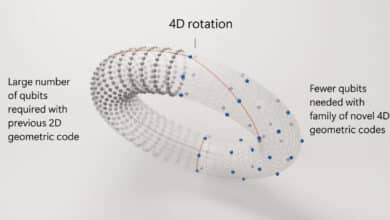

This noise asymmetry is not merely a curiosity. Theoretical work by Tuckett, Bartlett, Flammia, and Brown has shown that fault-tolerance thresholds for the surface code can exceed 5% under biased noise — far more forgiving than the standard ~1% threshold under depolarizing noise. The practical implication: silicon donor qubits may require significantly fewer physical qubits per logical qubit than architectures with symmetric noise, potentially reducing the overhead of quantum error correction by substantial margins.

For organizations tracking CRQC resource estimates, this is a factor that current models often overlook. The standard resource estimates — including Gidney’s RSA-2048 analysis and the Chevignard et al. ECC results — typically assume surface-code error correction with symmetric noise models. If silicon’s biased noise translates to lower overhead at scale, the physical qubit counts required for cryptanalytically relevant computations on silicon architectures could be meaningfully lower than current projections suggest. This is an area where the CRQC Capability Framework dimensions of “error correction overhead” and “noise characteristics” intersect in ways that generic threat models fail to capture.

Context: Silicon’s Logical Qubit Race

To understand where this result sits in the broader landscape, it helps to map the progression of silicon quantum computing milestones over the past several years.

In early 2022, multiple groups — Noiri et al. at RIKEN, Xue et al. at QuTech, Mądzik et al. at UNSW — demonstrated that individual silicon quantum gates could exceed the fault-tolerance threshold. In 2022, Philips et al. demonstrated universal control of a six-qubit quantum dot processor. The first attempts at quantum error correction in silicon came from Takeda et al. and van Riggelen et al., both in 2022, demonstrating phase-flip error correction through coherent conditional rotations.

Then the pace accelerated. In 2025, Thorvaldson et al. at SQC ran Grover’s algorithm on a four-qubit silicon processor above the fault-tolerant threshold. In October 2025, Diraq and imec demonstrated >99% gate fidelities in silicon spin qubits fabricated on 300 mm foundry wafers — proving that high-performance qubits could be manufactured using standard CMOS processes. In December 2025, SQC’s Edlbauer et al. unveiled an 11-qubit atom processor linking two phosphorus donor registers with gate fidelities ranging from 99.1% to 99.9% — the largest silicon donor processor to date.

In January 2026, the same SZIQA team published a companion paper in Nature Electronics demonstrating quantum error detection in silicon — using four nuclear spin qubits and one electron spin to detect arbitrary single-qubit errors with stabilizer measurements, achieving a four-qubit GHZ state fidelity of 88.5%.

The Nature Nanotechnology paper represents the next step in that sequence: moving from error detection to logical operations. It is the first time a silicon platform has demonstrated fault-tolerant logical state preparation, a universal logical gate set, magic state preparation above the distillation threshold, and an algorithm executed on encoded logical qubits. Superconducting circuits, neutral atoms, trapped ions, and nitrogen-vacancy centres in diamond had all previously demonstrated various forms of logical operations. Silicon had not — until now.

The China Dimension

The fact that this milestone comes from a Chinese laboratory — specifically the Shenzhen International Quantum Academy, a research institute established under the auspices of SUSTech and the Hefei National Laboratory — warrants attention beyond the technical achievement itself.

China’s quantum computing programme has historically been most visible in photonic and superconducting platforms (Jiuzhang and Zuchongzhi, respectively). The SZIQA team’s work demonstrates that Chinese researchers are now operating at the frontier of silicon quantum computing as well — a platform that, as I have noted in my coverage of quantum computing modalities, is uniquely positioned for eventual mass manufacturing due to its compatibility with existing CMOS fabrication infrastructure.

The strategic implications are worth considering. Silicon’s CMOS compatibility means that whoever achieves fault-tolerant silicon quantum computing first may be able to leverage semiconductor manufacturing capacity to scale far more rapidly than competing platforms. Australia’s SQC (backed by Michelle Simmons) and several European and U.S. groups — including Intel, Quantum Motion, and Diraq — have been the traditional leaders in silicon qubits. The SZIQA result introduces a well-resourced competitor operating at the same frontier. As the U.S. Intelligence Community’s 2026 Annual Threat Assessment made clear, quantum computing is now understood as a multi-dimensional strategic competition among at least five major nations.

What This Does NOT Mean

A few important boundaries around this result, to prevent overinterpretation:

This is not error correction. The [[4, 2, 2]] code is an error-detecting code, not an error-correcting one. It can identify that an error has occurred (and discard the corrupted measurement), but it cannot fix errors on the fly. True error correction — where errors are detected and corrected in real time through repeated syndrome measurements — has not yet been demonstrated in silicon. The researchers acknowledge this: they perform stabilizer parity projection through postprocessing, not mid-circuit measurements.

The logical qubit coherence times are shorter than the physical qubit coherence times. The average logical coherence time was approximately 208 μs, compared to ~523 μs for the constituent physical qubits. This is expected — a four-qubit entangled state is inherently more susceptible to decoherence than any individual qubit — but it underscores that encoding information logically does not automatically improve performance. The value of logical encoding comes from the ability to detect (and eventually correct) errors, not from inherent robustness.

Cross-talk remains the dominant error source. The close spectral proximity of some ESR driving frequencies in the donor cluster leads to unintended interactions between qubits, producing higher-weight errors that lie beyond the detection capability of the [[4, 2, 2]] code. The researchers identify this as the primary barrier to higher fidelities and note that improved donor engineering — specifically, more precise control over the atomic placement of phosphorus donors — is needed to mitigate it.

The read-out fidelity is modest. The average electron spin read-out fidelity for the working dot was estimated at approximately 81.45%, which introduces a systematic floor on all measurement-based characterizations. This is well below the >99% read-out fidelities achieved in some other silicon qubit implementations, suggesting significant room for improvement in the measurement chain.

What It Means for CISOs and Security Leaders

For the PostQuantum.com audience tracking quantum threat timelines, this result calibrates a specific cell in the CRQC development matrix.

Silicon spin qubits have always been the quiet contender in the quantum modality race — less flashy than superconducting qubits, less exotic than trapped ions, but with the unique advantage of potential CMOS-scale manufacturing. The constraint has been maturity: silicon lagged other platforms in demonstrating the logical operations required for fault-tolerant computation. This paper narrows that gap.

It does not change near-term threat timelines. The Gidney RSA-2048 estimate of ~1,400 logical qubits and the Chevignard et al. ECC results of ~1,100–1,200 logical qubits for elliptic curve attacks require not just logical qubits, but high-fidelity logical qubits operating at scale with real-time error correction. This experiment demonstrated two logical qubits with modest fidelities and postprocessed error detection. The gap between two and one thousand is not one that closes overnight.

But it does change the structural picture. Silicon now joins the roster of platforms that have demonstrated the fundamental building blocks of fault-tolerant computation. The biased noise profile offers a potential path to lower overhead than standard models predict. And the CMOS compatibility of donor-based silicon means that once the engineering challenges of precise atomic placement and cross-talk mitigation are solved, the scaling trajectory could be steeper than for platforms requiring bespoke fabrication.

The practical takeaway: if your quantum risk model implicitly assumes that “silicon is behind” and therefore contributes less to near-term threat, this paper suggests that assumption needs updating. The platform is behind in scale, but it has now demonstrated the correct set of primitives — and it is doing so in the architecture class uniquely positioned for leveraging the existing global semiconductor infrastructure.

Organizations that have not yet begun PQC migration cannot afford to wait for the modality race to produce a single winner. Every platform that demonstrates logical operations adds another potential pathway to a cryptanalytically relevant quantum computer. The responsible posture is migration now, hedged against architectural diversity — not bets on which platform will arrive last.

Looking Ahead

The researchers outline a clear roadmap: reduce cross-talk through better donor engineering and pulse optimization, fabricate donor cluster arrays to scale the system, and implement true fault-tolerant quantum computation architectures that exploit the high-connectivity Toffoli gates, biased noise, and cluster-encoded logical qubits demonstrated in this work.

The reference to a companion pre-print on “quantum computer based on donor-cluster arrays in silicon” (Zhang et al., arXiv:2509.24749) suggests the scaling work is already underway. The vision — modular arrays of donor clusters, each encoding logical qubits, interconnected through electron exchange coupling — aligns with the architecture that SQC has pursued from Australia but now has a parallel track in Shenzhen.

The first logical operations in silicon are a beginning, not an endpoint. But beginnings matter — especially when they happen in the material that built the classical computing industry, and especially when they happen simultaneously on two continents.

Quantum Upside & Quantum Risk - Handled

My company - Applied Quantum - helps governments, enterprises, and investors prepare for both the upside and the risk of quantum technologies. We deliver concise board and investor briefings; demystify quantum computing, sensing, and communications; craft national and corporate strategies to capture advantage; and turn plans into delivery. We help you mitigate the quantum risk by executing crypto‑inventory, crypto‑agility implementation, PQC migration, and broader defenses against the quantum threat. We run vendor due diligence, proof‑of‑value pilots, standards and policy alignment, workforce training, and procurement support, then oversee implementation across your organization. Contact me if you want help.