IBM Launches Heron R3 (ibm_pittsburgh): ~350 µS T2 and a Quality Upgrade for Its 156‑Qubit Platform

1 Aug 2025 – IBM has rolled out Heron r3, a new revision of its Heron processor family, debuting on the IBM Quantum Platform as ibm_pittsburgh in late July 2025. The headline change is quality, not scale: r3 keeps the 156‑qubit heavy‑hex design introduced with Heron r2, but IBM says targeted manufacturing improvements boost coherence, gate fidelity, and readout, including an ~350 µs T2 figure highlighted in the launch note.

Strategically, r3 reinforces IBM’s “iterate fast on physical‑qubit quality” approach as it targets quantum advantage by end‑2026 and a fault‑tolerant Starling system by 2029.

What IBM announced

In an IBM Quantum Platform product update, IBM announced ibm_pittsburgh, the first system powered by Heron Revision 3 (r3), hosted at its Poughkeepsie quantum datacenter. IBM positioned r3 as an engineering refinement rather than an architectural reboot, attributing the gains to “targeted improvements” that affect coherence, gate fidelity, and readout performance – and calling out an “industry-leading” ~350 µs T2 coherence (T1 was not specified in the announcement).

In the same note, IBM also retired an older Eagle‑family QPU (ibm_sherbrooke) and encouraged users to migrate to Heron‑based systems, citing ~5× lower error per layered gates (EPLG) and ~8× faster gates (relative to Eagle; r3‑vs‑r2 speedup was not specified).

What’s new in Heron r3 versus r2 and r1

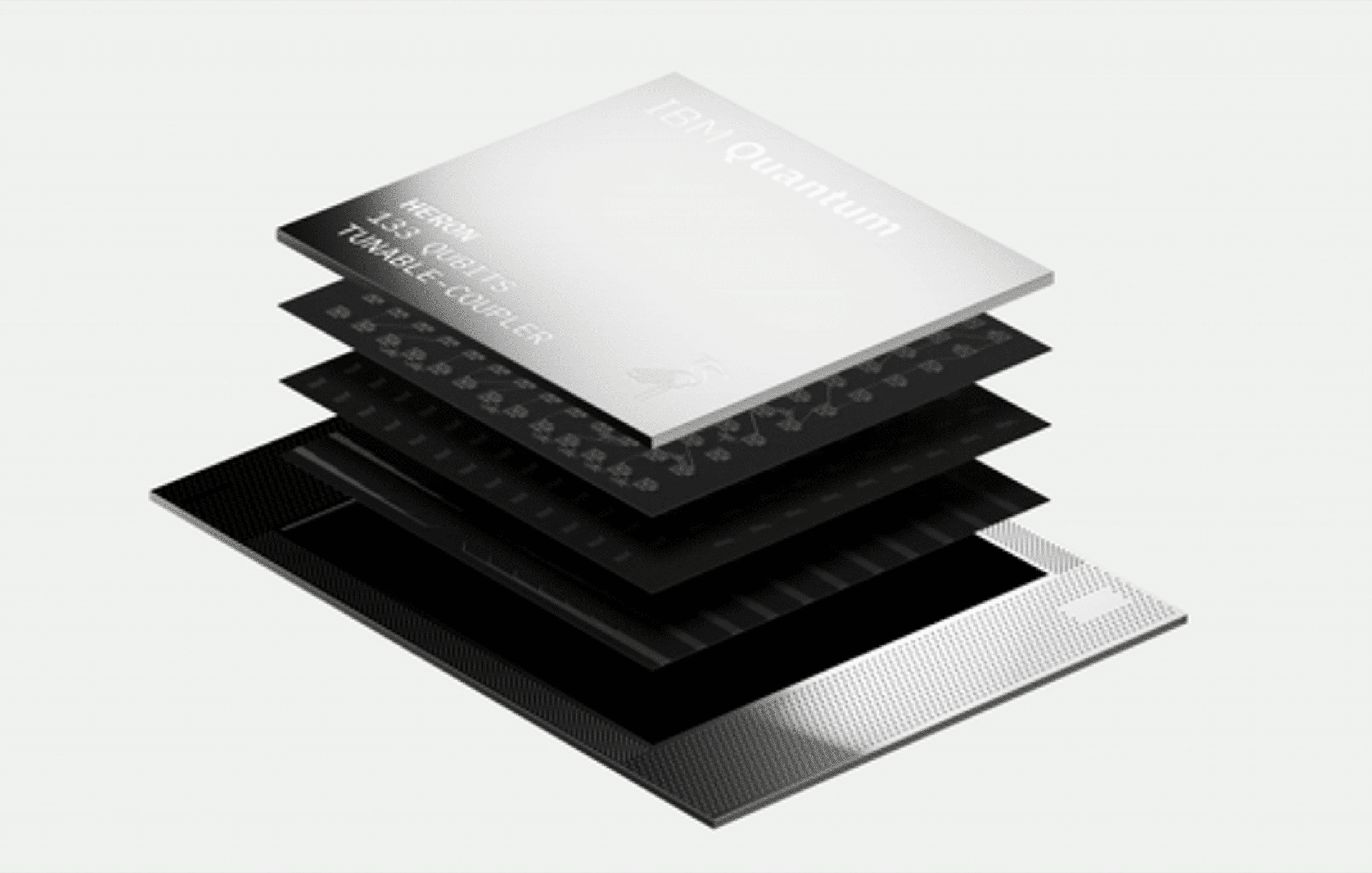

IBM’s own processor documentation frames Heron’s evolution as a sequence of revisions: r1 (Dec 2023) introduced the Heron family at 133 qubits; r2 (July 2024) redesigned the chip to 156 qubits in a heavy‑hex lattice and added a two‑level system (TLS) mitigation feature to stabilize coherence; and r3 (July 2025) focuses on manufacturing improvements to lift coherence/fidelity/readout.

Connectivity-wise, r3 inherits the same heavy‑hex constraints that shaped r1/r2: each qubit typically connects to two or three neighbors, trading raw connectivity for reduced crosstalk compared with denser lattices. IBM’s 2025 roadmap materials explicitly contrast this with its upcoming square‑lattice designs (four neighbors per qubit) planned to reduce compilation overhead for complex circuits.

On electronics and cryogenics, IBM continues to emphasize the “systems” side of scaling: Heron processors rely on high‑density signal delivery (including flex cabling) and sit within a broader platform that combines scalable cryogenics, runtime servers, and modular control electronics (especially in IBM Quantum System Two installations).

Notably, IBM did not announce any r3‑specific new fridge design or new control‑electronics generation in the r3 launch note; those elements appear as part of the ongoing System Two / datacenter strategy rather than an r3‑only shift.

On software and mitigation, the story is continuity. Heron r2 was publicly tied to major stack advances—IBM said improvements across Heron hardware plus Qiskit enabled certain circuit classes up to 5,000 two‑qubit gates, alongside a large speedup on a prior “quantum utility” workflow; IBM also highlighted mitigation tooling via Qiskit services and partner functions.

For r3, IBM’s primary messaging is that hardware quality improvements translate into better outcomes on the same kinds of metrics users track today (EPLG, readout error, throughput), rather than introducing a new mitigation feature analogous to r2’s TLS controls.

Heron r1, r2, r3 comparison table

| Spec | Heron r1 | Heron r2 | Heron r3 |

|---|---|---|---|

| IBM “revision” timing | Dec 2023 | July 2024 | July 2025 |

| Qubit count | 133 | 156 | 156 |

| Topology / connectivity | Heavy‑hex (2–3 neighbors typical) | Heavy‑hex | Heavy‑hex |

| Notable hardware add | Baseline Heron architecture | Adds TLS mitigation feature | Targeted manufacturing improvements |

| Coherence (T1) | Unspecified | Unspecified | Unspecified |

| Coherence (T2) | Unspecified | Unspecified | ~350 µs (IBM-highlighted) |

| Public “dashboard” snapshot: 2Q error (median)* | 2.46E‑3 | 2.03E‑3 | 1.52E‑3 |

| Public “dashboard” snapshot: readout error (median)* | 4.81E‑2 | 1.666E‑2 | 1.3E‑2 |

| Public “dashboard” snapshot: CLOPS* | 290K | 340K | 330K |

*Dashboard values are calibration‑ and fleet‑dependent snapshots from IBM’s public compute resources listing; they drift over time and vary by deployed system.

Revision definitions (dates/features) and the r3 T2 callout are from IBM’s processor documentation and r3 launch note.

Interpreting the table: r3 is best understood as quality compounding. The qubit count and lattice stay flat versus r2, but IBM is materially improving the “usable depth per qubit” ingredients – T2, readout, and effective two‑qubit error – which is precisely the direction that reduces the overhead (and cost) of eventual error correction.

Benchmarks and early signals from the community

IBM has not (in the r3 launch note) announced a new flagship “5,000‑gate‑class” result tied explicitly to r3; that milestone remains associated with the broader Heron + Qiskit improvements IBM publicized around r2.

What IBM has highlighted around r3 instead is benchmark progress on Quantum Volume (QV): Jay Gambetta reported ibm_pittsburgh surpassing QV thresholds at 1024 and 2048, and described AI‑optimized compilation reducing SWAP overhead when mapping dense all‑to‑all circuits onto Heron’s heavy‑hex topology.

How r3 advances IBM’s roadmap to 2029

IBM’s June 2025 roadmap update is explicit: by 2029, IBM aims to deliver IBM Quantum Starling, targeting ~200 logical qubits capable of executing 100 million quantum gates—a fault‑tolerant machine built as part of a modular, quantum‑centric architecture.

In that context, r3 is not “the step” to fault tolerance, but it is a necessary enabling step: higher coherence and lower errors reduce the physical‑qubit overhead required for any error‑corrected scheme, including IBM’s push toward qLDPC‑based architectures and real‑time decoding.

IBM’s published roadmap narrative also clarifies what comes next after Heron-class improvements: Nighthawk (square lattice, higher connectivity) is framed as a key platform on the route to quantum advantage by end‑2026, followed by Kookaburra (2026) and Cockatoo (2027) modules that build toward multi‑module fault tolerance, culminating in Starling milestones in 2028–2029.

Implications for quantum advantage, cryptography timelines, and the industry

For quantum advantage, r3’s significance is practical: better coherence/readout and lower effective two‑qubit errors make “utility‑style” experiments more repeatable and reduce the amount of mitigation/shot‑count inflation needed to extract signal, especially on constrained topologies like heavy‑hex.

However, IBM’s own roadmap messaging suggests that connectivity (and therefore compilation overhead) becomes the next binding constraint – hence the emphasis on square‑lattice designs and scaling circuit size toward the 15,000‑gate class later in the decade.

For cryptography, Heron r3 does not change the immediate risk calculus: breaking modern public‑key cryptography requires large‑scale, fault‑tolerant machines well beyond today’s physical‑qubit regimes. Even aggressive resource‑estimation work for RSA‑2048 still projects very large requirements under plausible assumptions (e.g., “noisy qubits” on grid architectures), despite rapid algorithmic improvements.

Quantum Upside & Quantum Risk - Handled

My company - Applied Quantum - helps governments, enterprises, and investors prepare for both the upside and the risk of quantum technologies. We deliver concise board and investor briefings; demystify quantum computing, sensing, and communications; craft national and corporate strategies to capture advantage; and turn plans into delivery. We help you mitigate the quantum risk by executing crypto‑inventory, crypto‑agility implementation, PQC migration, and broader defenses against the quantum threat. We run vendor due diligence, proof‑of‑value pilots, standards and policy alignment, workforce training, and procurement support, then oversee implementation across your organization. Contact me if you want help.