IBM Unveils 156-Qubit ‘Heron R2’ Quantum Processor

Table of Contents

Yorktown Heights, N.Y., USA (Nov 2024) – IBM has announced a new 156-qubit quantum processor called Heron R2, marking a significant upgrade to its quantum computing hardware portfolio. The Heron R2 chip is the second-generation follow-up to IBM’s 133-qubit “Heron” processor introduced in late 2023. Building on its predecessor, the Heron R2 not only adds more qubits but also delivers major improvements in qubit coherence, gate fidelity, and overall computational efficiency. IBM researchers report that the new system can execute quantum circuits with up to 5,000 two-qubit gate operations, nearly doubling the 2,880 two-qubit gate depth achieved in IBM’s 2023 benchmark. Thanks to these hardware upgrades and accompanying software optimizations, complex workloads that previously took over 120 hours to run on IBM’s best quantum machine can now be completed in roughly 2.4 hours – an almost 50× speedup.

IBM claims the Heron R2-based system is now powerful enough to tackle useful scientific problems in domains like materials science, chemistry, life sciences, and high-energy physics.

The Heron R2 was unveiled at IBM’s Quantum Developer Conference in November 2024 as the company’s latest effort to push quantum computing toward practical “utility scale” performance. The new processor features 156 superconducting qubits arranged in IBM’s signature heavy-hexagonal lattice topology. This represents a modest qubit count increase from the 133 qubits in the original Heron chip, but far more important are the qualitative improvements under the hood. IBM has emphasized that qubit quantity alone is only one factor – coherence time, gate quality, and circuit capacity often matter more for achieving useful results. On those fronts, the Heron R2 brings substantial gains. It retains the tunable coupler architecture introduced with Heron R1, which allows inter-qubit connections to be dynamically adjusted to minimize unwanted interactions. Additionally, the Heron R2 introduces new hardware-level noise mitigation, calibration refinements, and enhanced chip design techniques that together boost fidelity and stability across the processor.

Technical Advancements in the Heron R2 Chip

The Heron R2’s architecture incorporates several enhancements aimed at improving quantum hardware performance.

First, the qubit count has increased from 133 to 156 qubits, expanding the computational space available for quantum circuits. These qubits are patterned in a heavy-hexagonal lattice – a layout IBM uses in all its recent processors to maximize connectivity while reducing crosstalk. Each qubit is connected to its neighbors via tunable couplers, meaning the interaction strength between qubits can be turned up or down on demand. IBM pioneered this tunable coupler scheme in the original Heron as a means to suppress crosstalk (unwanted coupling) between qubits. In Heron R2, the tunable coupler design has been further refined and better calibrated to improve two-qubit gate operations. By effectively “decoupling” qubits when they are not actively interacting, the chip minimizes interference and can execute multi-qubit operations more reliably and in parallel. This results in higher-fidelity entanglement and fewer errors when performing logic gates across the processor.

One of the standout hardware features of Heron R2 is the addition of “two-level system” (TLS) mitigation technology to address microscopic noise sources. TLS noise arises from tiny material defects or impurities in the chip that can behave like extra two-level quantum systems, disrupting the qubits. IBM’s engineers have introduced a mitigation technique that actively controls the TLS environment, significantly reducing this source of decoherence. In practice, the TLS mitigation leads to improved qubit coherence times (the length of time qubits maintain quantum information) and greater stability of the processor’s performance over time. Together with the coupler-based crosstalk suppression, this means qubits in Heron R2 can retain high fidelity even as more qubits interact and as circuits run longer. IBM noted that these design changes led to measurable gains in gate accuracy – for example, updated calibrations earlier in 2024 improved the median two-qubit gate error rate on a Heron-class device from about $$5×10^{−3}$$ to $$3×10^{−3}$$ (i.e. from 0.5% down to 0.3%), a substantial boost in fidelity. Although specific device metrics for Heron R2 were not detailed in the announcement, IBM describes the chip as delivering “fast, high-fidelity two-qubit and single-qubit control” thanks to improved signal delivery and packaging innovations inherited from its Osprey (433-qubit) research. In essence, the Heron R2’s hardware advancements allow it to execute deeper and more complex quantum circuits with less error – enabling the leap to 5,000 gate operations per circuit demonstrated by IBM.

IBM also disclosed some architectural tweaks to gate operations in Heron R2 that further differentiate it from its predecessor. The processor natively supports a CZ (controlled-Z) two-qubit gate via its tunable couplers, a change from the cross-resonance (CX) gates used in earlier fixed-coupling designs. This native gate simplification, combined with what IBM calls “fractional gates,” reduces the number of pulses or steps needed to implement certain quantum operations. By executing more of a desired operation in a single analog step, the chip can accomplish the same logic with fewer sequential gates, which translates to lower error accumulation. IBM indicated that fractional gate implementations in Heron R2 help trim the circuit depth required for some algorithms, directly boosting effective fidelity. Furthermore, improvements in the qubit readout mechanism and cryogenic engineering provide cleaner measurements of qubit states. While specifics on readout fidelity were not given, it is expected to have improved alongside gate fidelity as IBM refined the chip fabrication and wiring. In fact, IBM adopted high-density flexible cabling and new packaging techniques (first tested in the Osprey chip) to deliver control signals to Heron qubits with minimal noise and signal loss. This level of hardware refinement – from materials and wiring to coupler tuning – results in a more noise-isolated and stable processor. The net effect is that Heron R2 can run longer quantum computations than before without decohering, a critical capability for pursuing quantum advantage in useful tasks.

Qiskit Software Updates Optimize Heron R2 Performance

Alongside the new Heron R2 chip, IBM rolled out major upgrades to its Qiskit quantum software stack aimed at extracting maximum performance from the hardware. These software improvements address everything from how quantum circuits are compiled and executed to how errors are mitigated in real time. One key focus has been on quantum error mitigation techniques integrated into Qiskit. As part of the Heron R2 launch, IBM highlighted the use of a tensor network error mitigation (TEM) algorithm within Qiskit, developed in partnership with startup Algorithmiq. This TEM method performs noise mitigation entirely in the classical post-processing stage – essentially filtering out errors from the raw results without adding extra quantum overhead. By leveraging classical tensor network simulations to model and cancel out noise, the TEM approach yields more accurate final results with fewer runs (shots) needed, compared to traditional error reduction methods. In practice, Qiskit can automatically apply such error-mitigation passes to results from Heron R2, helping to counteract the remaining noise on the 156-qubit device. Combined with the hardware’s built-in TLS noise suppression, these software-level mitigations significantly improve the reliability of deeper circuits executed on Heron R2.

IBM’s software enhancements also target the efficiency and speed of quantum circuit execution on the new processor. Over the past year, IBM redeveloped large parts of the Qiskit compiler (transpiler) and runtime engine to accelerate quantum workloads. The Qiskit transpiler – which translates abstract quantum programs into optimized low-level instructions for the hardware – has been supercharged. IBM rewrote the bulk of the transpiler in Rust, yielding up to a 60× improvement in compilation speed for complex circuits. The optimized transpiler not only runs faster, but also produces tighter circuits with fewer gates, thanks to smarter algorithms and AI-powered optimization passes. In fact, in tests presented at the conference, the latest Qiskit 1.3 transpiler achieved roughly 18–21% reductions in two-qubit gate count compared to the next-best competitor’s software. Moreover, IBM introduced a new cloud-based Qiskit Transpiler Service (currently in preview for select users) that applies additional AI-driven transpilation passes, further cutting circuit depth by up to 30% in some cases. These transpiler advances mean that quantum programs running on Heron R2 can be made more compact and efficient, directly increasing the effective circuit depth the hardware can handle before errors accumulate.

Another important upgrade is IBM’s next-generation Qiskit runtime, which orchestrates the execution of circuits on the quantum hardware and manages the hybrid quantum-classical workflow. Thanks to improvements in data movement and scheduling, as well as features like parametric compilation, the new system can achieve extremely high throughput on Heron R2. Parametric compiling allows users to compile a quantum circuit once and then repeatedly execute it with different parameter values (for example, rotating qubits by different angles in each run) without recompiling from scratch each time. This is especially useful for iterative algorithms and variational routines that adjust parameters over many cycles. By avoiding redundant compile steps and efficiently reusing circuits, IBM greatly reduced the overhead for such hybrid quantum-classical algorithms. The payoff is evident in a metric IBM calls Circuit Layer Operations Per Second (CLOPS) – essentially how many layers of a quantum circuit can be executed per second on the hardware+software stack. With Heron R2 and the upgraded runtime, IBM demonstrated 150,000+ CLOPS, a dramatic increase from about 37,000 CLOPS earlier in 2024 and a mere 950 CLOPS in 2022. This ~160× speed-up over two years stems from cumulative improvements in both hardware and software, allowing much faster cycling through quantum circuits. In practical terms, it enables near real-time quantum-classical hybrid operations: an algorithm can alternate between quantum computations on Heron R2 and classical computations on a CPU with minimal idle time. The low-latency coordination facilitated by the new runtime and scheduling software is a cornerstone of IBM’s “quantum-centric supercomputing” approach, in which quantum processors work in tandem with classical supercomputers. IBM has even developed specialized resource management tools (in collaboration with Rensselaer Polytechnic Institute) to integrate quantum systems with supercomputer job schedulers like SLURM, aiming for a seamless heterogeneous workflow between QPUs, CPUs, and GPUs. All these software advances – from faster compilers to smarter error mitigation – are tuned to amplify the raw capabilities of the Heron R2 chip, pushing the envelope of what can be computed on 156 qubits.

IBM also launched new Qiskit libraries and developer tools alongside Heron R2, underscoring the “easy-to-use” aspect of its strategy. The company announced Qiskit Add-ons (modular plugins for specialized algorithms) and an expanding Qiskit Functions Catalog, which offers pre-built function modules contributed by IBM and partners. For example, IBM provides functions for AI-driven circuit optimization and error suppression, while partners like Q-CTRL and Qunasys contribute functions for advanced error reduction and chemistry simulations, respectively. These high-level tools allow developers to leverage Heron R2’s power without needing to fine-tune every circuit detail. In summary, the Qiskit software stack has been holistically refined to support Heron R2, ensuring that users can run deeper circuits, mitigate errors, and integrate quantum computations into larger workflows more effectively than ever.

Heron R2’s Place in IBM’s Quantum Roadmap

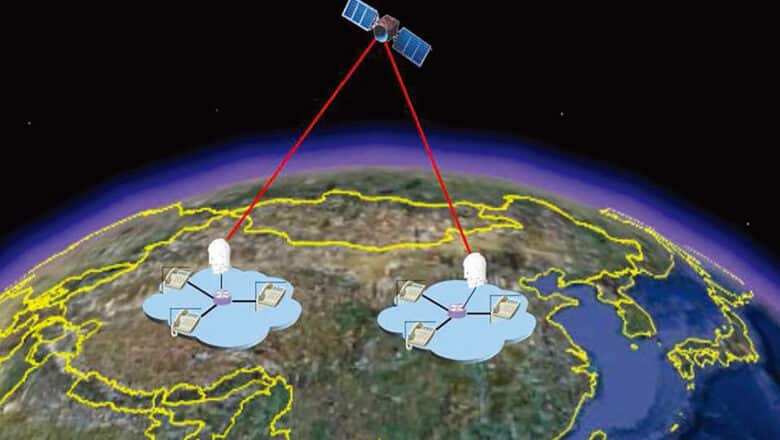

The introduction of the Heron R2 processor is a pivotal step in IBM’s multi-year quantum roadmap, which balances increasing qubit counts with improving qubit quality and scalability. IBM is positioning Heron R2 as the workhorse for the current era of “quantum utility”, where quantum computers can solve select problems faster or better than classical methods (even if they are not yet fully error-corrected systems). In IBM’s strategy, Heron-family processors form the building blocks of a modular quantum computing architecture. Notably, IBM’s Quantum System Two – the next-generation dilution refrigerator and system infrastructure unveiled in parallel with the original Heron – is designed to interconnect multiple Heron chips in one machine. The first IBM Quantum System Two, already installed in New York, contains three Heron R1 processors of 133 qubits each, for a combined 399 qubits of quantum resources in one system. This modular approach allows IBM to scale up total qubit count by linking chips, rather than putting all qubits on a single die. With the 156-qubit Heron R2, each module now packs more qubits with higher fidelity, enabling even more powerful configurations when multiple modules are connected. IBM researchers have demonstrated prototype setups (codenamed Flamingo) that use novel couplers to link two Heron chips over short distances (centimeters to a meter). This technology, shown at the Developer Conference, foreshadows IBM’s plan to deliver systems with >300 qubits by networking two Heron R2 processors together, and even larger multi-chip assemblages beyond that. By staying within the high-coherence, low-error regime of the Heron architecture while incrementally adding modules, IBM aims to scale quantum computers “like Lego blocks” – increasing size without compromising performance.

Crucially, Heron R2’s improvements in error rates and coherence support this modular vision. Since error-correction is not yet deployed on Heron-class devices, IBM relies on high native fidelity and error mitigation to get useful computations. The Heron R2 will serve as the primary platform for IBM’s near-term quantum applications and experiments, allowing researchers to push into problems that were previously intractable due to circuit depth or noise limits. Early results are promising: IBM and collaborators have already used Heron-class processors to explore chemistry simulations that were beyond brute-force classical methods. With Heron R2’s boost, such utility-scale algorithms can be run more efficiently, accelerating the pace of discovery. IBM’s roadmap calls for steadily increasing the capability of these modular systems each year, and Heron R2 is the latest evidence of that progress. It delivers on IBM’s 2022 challenge of running 100-qubit, 100-depth circuits in under 24 hours – now exceeding that target by executing 5,000-gate circuits in just a couple of hours. While IBM is concurrently developing larger chips (like the 1,121-qubit Condor for future error-corrected machines), the Heron series illustrates a focus on “quality over quantity” in the interim. In fact, the original Heron demonstrated a 5× lower error rate than the much bigger Condor prototype, reinforcing IBM’s choice to deploy Heron cores in System Two instead of the higher-qubit-count chips.

Quantum Upside & Quantum Risk - Handled

My company - Applied Quantum - helps governments, enterprises, and investors prepare for both the upside and the risk of quantum technologies. We deliver concise board and investor briefings; demystify quantum computing, sensing, and communications; craft national and corporate strategies to capture advantage; and turn plans into delivery. We help you mitigate the quantum risk by executing crypto‑inventory, crypto‑agility implementation, PQC migration, and broader defenses against the quantum threat. We run vendor due diligence, proof‑of‑value pilots, standards and policy alignment, workforce training, and procurement support, then oversee implementation across your organization. Contact me if you want help.