Silicon’s First Attempts at Self-Repair: Phase-Flip Error Correction Demonstrated in Semiconductor Spin Qubits

Table of Contents

25 Aug 2022 – Seven months ago, three teams simultaneously proved that silicon spin qubits could operate above the fault-tolerance threshold — the quality of individual gates good enough, in principle, for error correction to work. That was the prerequisite. Now comes the thing itself. Two independent groups have demonstrated quantum error correction in semiconductor spin qubits for the first time. Takeda et al. at RIKEN, publishing in Nature, implemented a three-qubit phase-flip correcting code using electron spin qubits in silicon quantum dots — the same platform and the same group (Seigo Tarucha’s lab) that delivered one of the three threshold-crossing results in January. Separately, van Riggelen et al. at QuTech, publishing in npj Quantum Information, demonstrated a phase-flip code using a four-qubit array of hole-spin qubits in germanium — a closely related semiconductor platform.

Neither result achieves fault-tolerant error correction. Both groups are candid about the limitations. But they establish that the conceptual machinery of quantum error correction — encoding, error detection, and conditional correction — can be implemented in semiconductor spin qubits. For a platform whose primary selling point is eventual CMOS-scale manufacturing, getting error correction to work at all, even imperfectly, is a milestone that matters.

The RIKEN Result: A Three-Qubit Code With a One-Step Toffoli

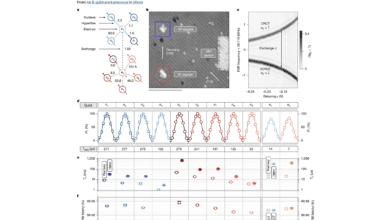

The Takeda et al. experiment uses three electron spin qubits confined in a triple quantum dot array in a Si/SiGe heterostructure. The three-qubit phase-flip code is the simplest non-trivial error-correcting code: it encodes one logical qubit across three physical qubits and can correct a phase-flip (Z) error on any single qubit.

The circuit proceeds in three stages. First, the logical state is encoded by entangling the three qubits using CNOT gates and Hadamard rotations, spreading the quantum information across all three. Second, a phase-flip error may occur (either naturally through decoherence or deliberately injected). Third, the error is decoded and corrected.

The correction step is where the RIKEN team introduced a notable innovation: a single-step resonantly driven iToffoli gate — a three-qubit conditional rotation that performs the error correction in one pulse rather than decomposing it into a sequence of single- and two-qubit gates. This is significant because gate decompositions add depth and therefore additional opportunities for error. The single-pulse Toffoli keeps the correction circuit compact.

The results show that the error correction protocol does mitigate both deliberately introduced single-qubit phase-flip errors and the intrinsic dephasing from quasi-static noise in the system. The encoded state maintains higher fidelity with the correction protocol than without it — the signature of working error correction.

However, the protection is limited. The code only corrects phase-flip errors, not bit-flip errors or arbitrary errors. And the overall fidelities, while improved by the correction, remain below what would be needed for repeated error correction cycles in a fault-tolerant architecture. The paper is honest about this: it describes the result as a “successful implementation of QEC” and a demonstration of “the potential” of the platform, not a claim of fault-tolerant operation.

The QuTech Result: Phase-Flip Code in Germanium

The van Riggelen et al. experiment takes a different approach in a related material system. The qubits are hole spins in a planar germanium (Ge/SiGe) quantum dot array — four qubits arranged in a linear chain. Germanium hole-spin qubits have the advantage of strong spin-orbit coupling, which enables all-electrical control without micromagnets, and the absence of valley degeneracy that complicates some silicon electron-spin implementations.

The team demonstrated both a two-qubit and a three-qubit phase-flip code. For the three-qubit version, they constructed a Toffoli-like gate from a combination of controlled-Z and controlled-S⁻¹ gates — a more conventional decomposition than RIKEN’s single-pulse approach, but one that demonstrates the composability of the gate set.

The key result: the protocol preserves the state of the data qubit against phase-flip errors by encoding it across the ancilla qubits and applying a refocusing pulse. The team notes, however, that “both the quality and quantity of the qubits will require significant improvement to achieve fault-tolerance.” This is an unusually direct assessment, and it is correct: the gate fidelities in the germanium system are below the fault-tolerance threshold, meaning the error correction adds more errors than it fixes. The experiment demonstrates the protocol, not the performance.

What These Results Mean — and Don’t Mean

The honest assessment of both papers is that they demonstrate the procedure of quantum error correction in semiconductor spin qubits, but not the performance needed for it to provide a net benefit in a fault-tolerant architecture. This is not unusual for first demonstrations — early superconducting and trapped-ion error correction experiments had similar characteristics — but it is important to state clearly.

What they do establish:

First, that three or more semiconductor spin qubits can be coherently controlled together with enough fidelity to execute an error correction circuit. This was not a given. Error correction circuits are deeper and more complex than individual gate benchmarks, and the transition from benchmark quality to circuit quality is where many platforms struggle.

Second, that the dominant error type in these systems — dephasing (phase-flip) — is precisely the type that the simplest codes are designed to correct. This is fortunate. If the dominant errors had been harder to correct (say, correlated multi-qubit errors), the path to fault tolerance would be much steeper.

Third, that different flavours of semiconductor spin qubits — electron spins in silicon (RIKEN) and hole spins in germanium (QuTech) — can both implement error correction protocols. This breadth suggests that error correction is compatible with the semiconductor platform generally, not just with one specific implementation.

The Path Forward

These results sit in the early part of a long progression. The next milestones for semiconductor spin qubit error correction include:

Implementing a code that corrects arbitrary single-qubit errors — not just phase-flips. This requires either a more complex code (such as the [[4, 2, 2]] error-detecting code or the five-qubit code) or a concatenation of phase-flip and bit-flip correcting codes.

Demonstrating that error correction provides a net benefit — that the encoded logical qubit retains fidelity better than the best unencoded physical qubit. This is the “break-even” point, and it requires physical gate fidelities well above threshold.

Moving from coherent correction (applying a unitary gate to fix the error) to measurement-based correction (measuring a syndrome, classically processing the result, and applying a conditional correction in real time). Measurement-based error correction is what scalable fault-tolerant architectures require, and it demands capabilities — fast mid-circuit measurement, real-time classical processing, conditional feedback — that semiconductor spin qubits have not yet demonstrated.

For security professionals tracking the CRQC trajectory, these experiments do not change timelines. But they establish that silicon is following the same developmental sequence as superconducting qubits and trapped ions — threshold crossing, then error correction, then scaling. The platform is three to five years behind the leaders on this sequence, but it is on the same track. And silicon’s unique advantage — the ability to leverage semiconductor manufacturing for scale — becomes relevant precisely when the platform reaches the engineering phase of error correction.

The first attempts at self-repair are never pretty. They are, however, essential.

Quantum Upside & Quantum Risk - Handled

My company - Applied Quantum - helps governments, enterprises, and investors prepare for both the upside and the risk of quantum technologies. We deliver concise board and investor briefings; demystify quantum computing, sensing, and communications; craft national and corporate strategies to capture advantage; and turn plans into delivery. We help you mitigate the quantum risk by executing crypto‑inventory, crypto‑agility implementation, PQC migration, and broader defenses against the quantum threat. We run vendor due diligence, proof‑of‑value pilots, standards and policy alignment, workforce training, and procurement support, then oversee implementation across your organization. Contact me if you want help.