Capability D.2: Decoder Performance (Real‑Time Error Correction Processing)

Table of Contents

This piece is part of an ten‑article series mapping the capabilities needed to reach a cryptanalytically relevant quantum computer (CRQC). For definitions, interdependencies, and the Q‑Day roadmap, begin with the overview: The CRQC Quantum Capability Framework.

(Updated in Nov 2025)

(Note: This is a living document. I update it as credible results, vendor roadmaps, or standards shift. Figures and timelines may lag new announcements; no warranties are given; always validate key assumptions against primary sources and your own risk posture.)

Introduction

Direct CRQC Impact: Critical – often described as the nervous system of a fault-tolerant quantum computer. Decoder performance refers to the classical system’s ability to process quantum error syndromes (Capability B.2) and correct errors in real time. Without a fast and accurate decoder running alongside the quantum hardware, even the best quantum error-correcting code (QEC) cannot function.

In a fault-tolerant quantum computer, qubits are continuously monitored via stabilizer measurements (producing “syndrome” bits) to detect errors (Capability B.2). The decoder is a classical algorithm (running on specialized hardware) that takes this rapid stream of syndrome data and figures out which qubits have experienced errors, so that corrections can be applied immediately.

Achieving real-time decoding at scale is enormously challenging: a CRQC may need to handle millions of physical qubits, with syndrome measurements every ~1 microsecond. That translates to an error data rate on the order of 106 syndrome bits per microsecond across the machine – tens of terabytes of data per second that must be processed on the fly. The decoder must not only keep up with this torrent of data without backlog, but also make near-optimal decisions to minimize logical errors.

What It Is: The Decoder in Quantum Error Correction

In essence, the decoder is the real-time decision engine of quantum error correction (Capability B.1). Every cycle (typically ~1 µs in leading platforms) the quantum hardware performs a round of stabilizer measurements, yielding a pattern of binary outcomes called the syndrome. These syndromes indicate the parity of certain qubit groupings and thus contain clues about where an error (bit-flip or phase-flip) may have occurred. It’s the decoder’s job to interpret this syndrome pattern and determine which physical qubits, if any, need corrective action. If the decoder deduces that a particular qubit suffered an X error, for example, it will instruct the control system to flip that qubit (applying another X gate) to correct it. In cases where the pattern of syndromes corresponds to a full logical error (meaning the error cannot be corrected and has corrupted the encoded qubit), the decoder flags a failure.

Crucially, the decoder must perform this inference faster than the QEC cycles themselves. Quantum error correction is a continuous, streaming process – every microsecond (or whatever the cycle time is), a new batch of syndrome bits arrives that needs decoding. If the decoder takes too long to process one round, subsequent rounds will pile up, causing a backlog. In theoretical threshold analyses of QEC in the 1990s and 2000s, researchers often assumed that classical processing could be done “instantaneously” or that it was not a bottleneck. In practice, however, executing a complex decoding algorithm in under a microsecond is a serious computing challenge, especially as the number of qubits (and hence syndrome bits) grows.

Decoder algorithms: A variety of algorithms have been developed to perform syndrome decoding. Many map the problem to a graph: each error can cause a certain syndrome pattern (often visualized as pairs of “defects” that need to be matched). A common approach for the popular surface code is the minimum-weight perfect matching (MWPM) decoder, which uses a graph algorithm (like Edmonds’ blossom algorithm) to pair up syndrome defects in a way that likely corresponds to actual error paths. MWPM was introduced in the context of QEC by Dennis, Kitaev, and co-workers in the early 2000s and later refined by Fowler and others, achieving error thresholds around the ~1% level for circuit-level noise (and ~3% for simpler noise models).

Another class of decoders is the union-find decoder, an algorithmic approach that achieves similar accuracy to MWPM but with lower complexity, proposed in the late 2010s to speed up surface-code decoding. There are also decoders based on belief propagation (inspired by classical LDPC code decoders) and even machine learning approaches. Accuracy is paramount – a decoder should correctly identify errors most of the time, otherwise those missed or mis-corrected errors will accumulate and cause the logical qubit to fail. The best decoders today come quite close to the theoretical optimum error suppression for a given code, meaning the primary remaining challenge is speed and integration, rather than inventing drastically more accurate algorithms.

Latency vs. accuracy: Decoder performance thus has two facets – accuracy (how close to optimal error-correction it is, which affects the effective logical error rate) and latency or throughput (how fast it can process syndromes, usually measured in cycles per second or equivalently the time per decode). For a CRQC, the decoder must be both highly accurate (to keep logical error rates extremely low over billions of operations) and ultra-low latency (able to keep up with perhaps a million syndrome bits per second per logical qubit, across thousands of logical qubits). As a concrete figure, if each QEC cycle is 1 µs, the decoder has on the order of one microsecond to interpret each round of data from the entire system – essentially a megahertz-class computation that cannot ever pause. This is a formidable requirement, and it’s why special-purpose classical hardware (FPGAs, ASICs, or GPUs used in certain ways) is necessary. Traditional CPUs or software running on a PC would be far too slow and would introduce unpredictable latency due to operating system overhead.

Role in CRQC: Why Fast Decoding is Critical

Decoder performance is mission-critical for scaling to a cryptographically relevant quantum computer. It’s often said that quantum error correction involves a hybrid of quantum and classical processes – the quantum hardware does the delicate quantum operations and measurements, but a classical digital system must interpret results and feed back corrections in real time. In this sense, the decoder is the brain or nervous system of a fault-tolerant quantum computer, taking sensory input (syndromes) and triggering reflexive responses (error corrections) constantly. If that classical brain lags or gives the wrong instructions, the whole system fails to maintain the quantum logic.

One major issue is the “backlog problem.” This occurs if the syndrome data is produced faster than the decoder can handle it. Imagine if every microsecond your quantum chip produces a new chunk of data, but your decoder takes 5 microseconds to process each one – the unprocessed data would queue up endlessly. In a fault-tolerant circuit with feedback (where later operations might depend on previous correction outcomes), a backlog forces later operations to wait, causing an ever-growing delay that can exponentially slow down the computation. In effect, the quantum computer would stall out or be forced to operate at the pace of the slow decoder, negating any advantage. To avoid backlog, the decoder’s throughput must exceed the syndrome generation rate. For superconducting qubit platforms, that means decoding faster than about 1 million syndrome cycles per second. Similar or even more stringent requirements hold for other platforms as they scale up (ion trap cycles might be slower, but future neutral-atom or photonic QEC systems could also produce massive parallel syndrome data).

The decoder’s speed is not just about keeping pace; it also influences how one designs the quantum system. For example, code distance (the size of the error-correcting code) is a double-edged sword: a larger distance means more physical qubits and more stabilizer measurements per cycle (hence more bits to decode each round), but it also offers higher potential error suppression. If you have a very fast decoder, you might afford to use a larger code (distance 25 or beyond) to get ultra-low logical error rates, confident that the decoder can handle the heavier workload. Conversely, if decoding was a bottleneck, engineers might be forced to use smaller codes or insert idle time between QEC cycles, which would severely hurt the overall error-correction performance. In short, decoder performance sets a ceiling on how effective QEC can be – a slow decoder can squander the benefits of good qubits and good codes by failing to correct errors promptly.

Another critical role of the decoder emerges when performing non-Clifford operations in a fault-tolerant manner. Certain high-level operations (like magic state injection (Capability C.2) or lattice surgery between logical qubits) require conditional steps – e.g. measuring a qubit to teleport a state, then applying a correction to another qubit depending on the measurement outcome. In a surface code implementation, performing a logical T-gate (a common non-Clifford gate) involves such conditional logic: you measure an ancilla and must apply a corrective operation if the outcome is 1, for instance. This means the decoder must not only correct generic noise, but also quickly provide the result of specific syndrome-based measurements that determine how the algorithm proceeds (a concept sometimes called logical branching). Typically, there is a limited time window (on the order of a few microseconds at most) to enact these feed-forward decisions before the quantum state decoheres or before the next steps must begin. If the decoder cannot deliver the needed answer (was that logical operation successful, do we need to apply a Z correction?) within that window, the execution of the algorithm will be delayed or error-prone. Thus, real-time decoding is a prerequisite not just for error correction, but for performing a sequence of fault-tolerant operations at full speed (Capability D.1).

Finally, decoder accuracy has a direct impact on the effective error rates of the logical qubits. A perfect code with an optimal decoder can in theory suppress errors exponentially with the code size. But a sub-optimal decoder might miss certain error combinations or occasionally output a wrong correction, leading to a logical fault where an optimal decoder would have succeeded. In practice, leading decoders like MWPM or advanced union-find approaches get very close to the optimal threshold of the surface code. Nonetheless, ongoing research continues to improve decoding algorithms so that logical error rates can be pushed even lower without exorbitant overhead. For a CRQC aiming to run billions of operations, even a small difference in decoder accuracy (and thus logical error rate) can mean the difference between needing, say, distance 21 vs. distance 25 code – which could save hundreds of thousands of physical qubits. In summary, fast and accurate decoders maximize the mileage we get out of each physical qubit and are as indispensable as the qubits themselves in the quest for large-scale quantum computing.

Status and Recent Progress in Decoder Technology

Despite the daunting requirements, decoder technology has advanced rapidly in recent years, leveraging progress in both algorithms and classical computing hardware. It’s an area where quantum computing meets classical high-performance computing. Below we outline key milestones and the current state of the art:

Foundational work (1990s – 2000s)

Quantum error correction itself was born in the mid-1990s, with Shor and Steane’s papers introducing the first QEC codes and demonstrating that quantum information can, in principle, be protected from errors. Early fault-tolerance theory (the threshold theorem) showed that if physical error rates are below a certain threshold and if errors are corrected faster than they accumulate, one can achieve arbitrarily long quantum computations. In these theoretical treatments, the existence of a sufficiently fast decoder was often just assumed (e.g. “polynomial-time classical computation can be executed instantaneously” in threshold proofs). The first decoders were relatively simple, since early codes like the Shor or Steane codes had few qubits.

As attention shifted to more scalable codes like the surface code (pioneered by Kitaev and analyzed by Dennis et al. in 2002), researchers formulated decoding as a matching problem on a 3D lattice. By ~2006-2012, improved classical algorithms made it feasible to simulate larger codes: minimum-weight perfect matching became a workhorse decoder, with Fowler, Wang, and others demonstrating surface-code error thresholds around ~1% per gate for realistic noise using this approach.

These results gave confidence that, at least in simulation, decoders could handle hundreds of qubits and correct errors reliably under threshold conditions.

Prototype decoders and algorithms (2010s)

Throughout the 2010s, a variety of decoders were developed. Renormalization group decoders, belief propagation variants, and later machine-learning-based decoders were explored. A notable development was the union-find decoder (circa 2017-2018), which offered an almost linear-time decoding method for surface codes without significant loss of accuracy compared to MWPM. This was important because MWPM, while optimal, can be computationally heavy (worst-case polynomial time that grows quickly with code distance). Union-find uses a disjoint set data structure to quickly cluster syndrome defects and correct them, enabling much faster decoding in large codes.

By the late 2010s, decoding algorithms had matured to the point that software implementations (e.g. PyMatching, an optimized matching decoder library) could handle moderate-size codes on standard processors for experiment post-processing. However, doing this in real time with sub-microsecond latency was another matter – that required moving to customized hardware solutions.

Hardware acceleration (2020-2022)

Quantum hardware began approaching the scale where real-time decoding feedback loops were needed. Superconducting qubit systems, for instance, improved coherence and gate speeds to the point of running small error-correcting codes (distance-3 or distance-5 surface codes) in experiments. Classical computing companies and startups recognized the decoder bottleneck and started adapting hardware for the task. GPUs (graphics processors) were tried for offline decoding – NVIDIA even released tools like CUDA-Q QEC to speed up decoding computations on GPUs, achieving over 30× speedups in some decoding tasks. But GPUs, which excel at parallel throughput, often have high latency in communicating with quantum hardware (the data transfer and scheduling overheads are too slow for microsecond cycles).

Attention thus shifted to FPGAs (Field-Programmable Gate Arrays) – reconfigurable chips that can be programmed to perform the decoder algorithm in dedicated logic circuits. FPGAs can provide deterministic, low-latency processing by hardwiring the algorithm into hardware, trading off some flexibility for speed. By around 2021-2022, labs began testing FPGA-based decoders. For example, teams from companies like Riverlane and university groups built FPGA prototypes that could decode a surface-code patch faster than the experiment cycle time. Riverlane reported FPGA decoders hitting sub-20 µs latency for a full round of decoding on small code patches.

Other quantum hardware vendors, including IBM and Xanadu, also integrated FPGAs into their control systems for scalable, real-time decoding, with some systems architected to handle up to thousands of physical qubits worth of syndrome data.

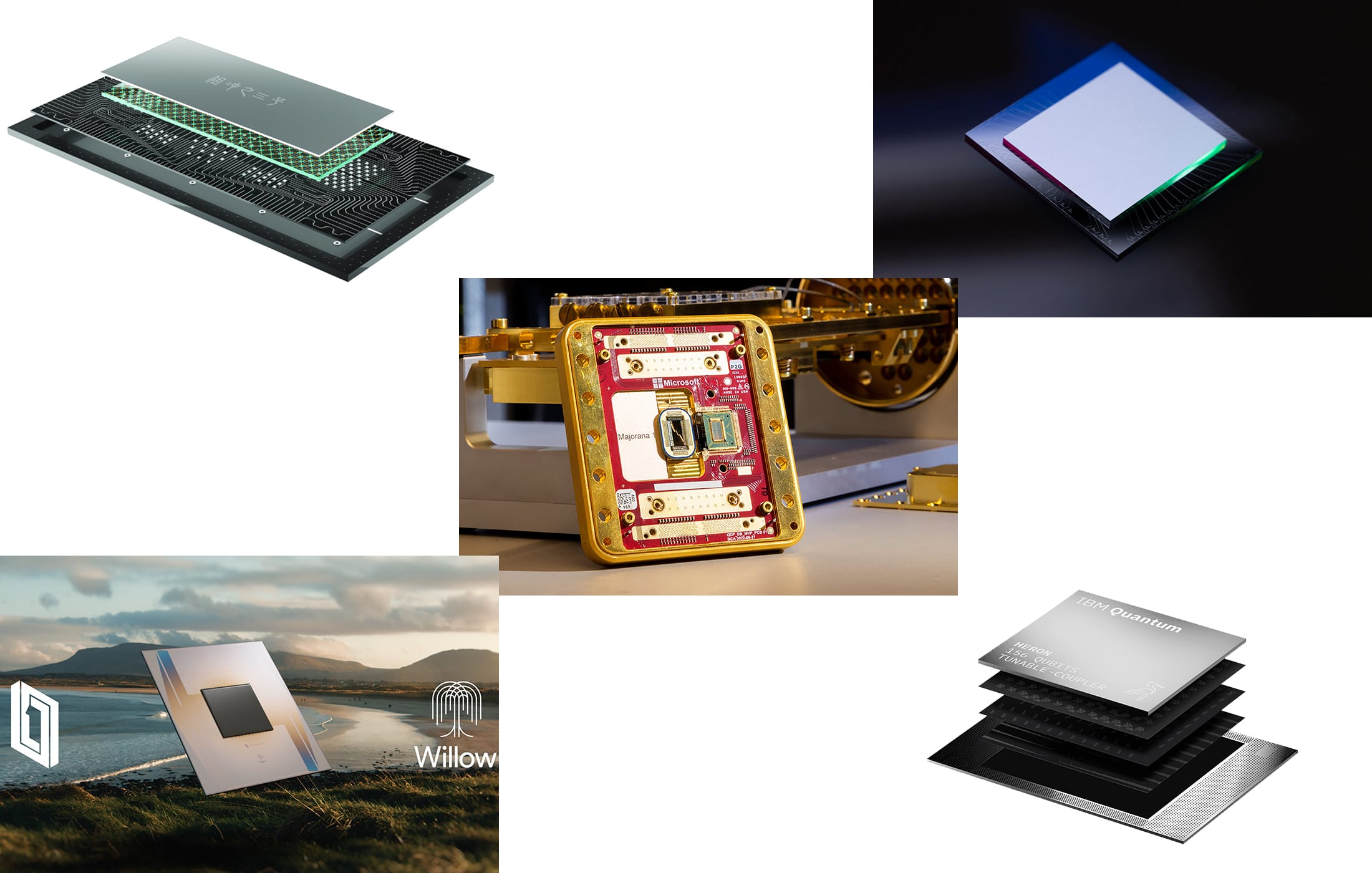

Recent breakthroughs (2023-2024)

The past two years have seen landmark demonstrations of real-time quantum error correction with fast decoders, as well as record-breaking decoder hardware performance. In late 2023, Google’s Quantum AI team demonstrated for the first time a logical qubit that outperformed its constituent physical qubits, using a distance-5 surface code. This was a historic proof that QEC works on real hardware (logical error rate was lower than physical error rate), albeit at small scale. Google’s experiment used a software decoder (running on a classical computer) in a streaming fashion. The decoder was essentially working in post-processing or parallel to the experiment with a latency on the order of seconds (not microseconds), so it wasn’t feeding back corrections in real time during circuit operation. That was fine for demonstrating error suppression, but it’s not sufficient for a future CRQC where continuous operation is needed.

Complementing that achievement, Riverlane and Rigetti announced in 2024 the world’s first low-latency QEC experiment on hardware. They integrated an FPGA decoder directly into Rigetti’s 84-qubit superconducting system (Ankaa-2) and performed an 8-qubit “stability” experiment – essentially a small repetitive error-correcting code – with the decoder correcting errors on the fly. The decoder achieved a mean processing time per round below 1 µs (under a microsecond) over 25 cycles, successfully keeping up with the device’s 1 µs cycle time. This real-time feedback prevented any backlog even on a fast superconducting platform, and they observed that increasing the number of QEC rounds led to exponential suppression of errors as expected. Furthermore, they demonstrated a fast feedback loop involving a conditional operation: a sequence of 9 QEC rounds followed by a decoder-informed conditional step was executed with a total latency of only 9.6 µs. This shows that even the branching logic (where the quantum program waits for a decoder’s decision) can be done within ~10 µs, meeting the needs of magic state injection and other non-Clifford operations that require quick classical decisions.

High-speed ASIC decoders

Perhaps the most impressive decoder performance numbers have come from specialized hardware implementations. In late 2024, researchers (including the Riverlane team) unveiled a custom decoding chipset based on a Collision Clustering (CC) decoder algorithm, tested on both FPGA and ASIC (application-specific integrated circuit) platforms. According to a January 2025 report, their FPGA prototype decoded an 881-qubit surface code in 810 nanoseconds, and a custom ASIC version decoded a 1,057-qubit code in just 240 ns – that’s over 4 million syndrome bits processed per second with one chip. These speeds are well into the megahertz regime needed for large-scale QEC.

Equally important, the ASIC was extremely compact (0.06 mm²) and consumed only ~8 mW of power, making it feasible to place such decoder chips near the cryogenic quantum hardware (potentially even at cold temperature) without overwhelming the cooling system. The achievement was published in Nature Electronics and set a new standard for decoder throughput and efficiency, indicating that dedicated silicon can handle thousand-qubit-level decoding tasks in real time.

This is a crucial proof-of-concept that hardware decoders can scale to the sizes required by a CRQC.

Status summary

As of early 2025, we have: (1) validated decoder algorithms (MWPM, union-find, etc.) that work well up to at least moderate code sizes, with known thresholds and performance; (2) FPGA decoders integrated in actual quantum experiments at patch scale (tens of qubits), achieving sub-microsecond latencies ; and (3) ASIC decoder prototypes demonstrating the raw speed and low power needed for ~1000 qubit-scale decoding tasks.

The concept is proven and small-scale implementations have been shown to meet the necessary speed requirements. What remains is to scale up and integrate these decoders into full systems. So far, continuous decoding has been shown for at most on the order of 10-100 qubits in real hardware tests.

The gap to CRQC is demonstrating that we can decode hundreds of thousands or millions of qubits’ worth of syndrome data in real time, continuously, for days of operation, with no degradation or crashes. That will likely involve networking many decoder units or developing hierarchies of decoders to share the load, as well as ensuring the entire control system (not just the raw decode logic) can handle the I/O and timing at scale.

It’s worth noting that decoder R&D is a very active field. In just the last year or two, multiple organizations – from startups to big tech – have made decoder development a priority. For example, IBM has discussed new decoder approaches (like a recently publicized “Relay-BP” decoder, combining belief propagation with novel techniques) to improve speed and reliability. Academic groups are exploring adaptive decoders that adjust to noise changes, and decoders tailored for other QEC codes (such as quantum LDPC codes that might offer advantages in overhead). However, the surface code with matching/uniform decoders remains the leading paradigm, and all the progress discussed above directly boosts confidence that a surface-code-based CRQC can have a decoder that keeps up.

Key Interdependencies and Challenges

Decoder performance does not exist in a vacuum – it’s tightly interwoven with many other aspects of the quantum computing stack. Here are the major interdependencies and considerations:

Syndrome Extraction Hardware

The decoder is only as good as the data it receives. The syndrome bits come from measurements (Capability B.2) of ancilla qubits on the quantum processor. If those measurements are slow or inaccurate, the decoder’s job becomes harder. For instance, superconducting qubits can perform readout in a few hundred nanoseconds to a microsecond; trapped-ion qubits might take longer per measurement. Faster measurements mean a higher data rate for the decoder to ingest.

Furthermore, measurement errors themselves must be handled by the decoder (typically by treating consecutive rounds of syndrome to identify spurious flips). The decoder design often assumes a certain error model for syndrome bits. In practice, tight integration between the quantum hardware and decoder is needed – e.g. the decoder might need calibration data about typical error rates to perform optimally. Any changes in the quantum circuit timing or the noise environment could necessitate re-tuning the decoder algorithm or parameters. This has led some to propose that decoders might eventually include machine learning components to adapt to changing noise.

Classical Computing Infrastructure

Decoding a million-qubit quantum computer in real time is a massive classical computing problem. It has been projected that error correction for a full-scale machine could involve processing on the order of 100 terabytes of data per second in the worst case. This means that not only the core decode algorithm, but also the data movement (getting syndrome bits from the qubit control electronics into the decoder and then sending back correction signals) is a huge engineering challenge. Most likely, a distributed network of decoders will be required – perhaps one dedicated FPGA/ASIC per region of the chip, or a tree of decoders that handle local patches and then communicate for global decisions. The latency of interconnects and communication between these sub-decoders could become a bottleneck if not carefully designed. Some experimental setups are exploring cryogenic electronics (classical chips operating at 4 K or even sub-Kelvin temperatures alongside the qubits) to cut down communication latency. Low-power decoder ASICs (like the 8 mW one above) might be placed on the cold stage so that syndrome data doesn’t have to travel up to room temperature, thus shaving off a few microseconds of cable delay. However, cryo deployment means strict power and heat limits – which is why power-efficient decoder designs are important.

Continuous Operation and Reliability

A CRQC may need to run for days (e.g. ~5 days to break RSA-2048 by some estimates). This means the decoder hardware and software must run essentially without interruption or error for that entire time. A crash or malfunction in the classical decoder mid-run would be catastrophic (it could cause the quantum computation to fail or at least lose synchronization). Therefore, the decoder systems must be highly reliable and tested for long uptimes. Techniques from classical high-performance computing, like redundancy and error-checking in the decoder logic, might be needed to ensure that even cosmic ray flips or other rare events don’t stop the decoder.

This is a new kind of challenge: we’re talking about building classical compute engines that can run real-time, streaming processes for days on end (Capability D.3), something more akin to a mission-critical embedded system than a typical computer program.

QEC Code and Protocol Choices

The requirements on the decoder also depend on what error-correcting code and protocol the quantum computer uses. The surface code, for example, has the advantage of a regular structure that allows local, nearest-neighbor syndrome extraction – making it amenable to efficient decoders like matching. Other codes (like certain quantum LDPC codes or concatenated codes) might have different decoder designs (some easier, some harder). If future research finds codes that drastically reduce overhead (qubit count), one must ensure decoders exist for them that can run fast.

There’s an interdependency particularly with so-called “single-shot” error correction protocols, where one round of syndrome might suffice if processed cleverly.

Some advanced schemes (and recent research like Algorithmic FT or AFT protocols) aim to reduce the number of syndrome rounds per logical operation.

These approaches can ease the decoder throughput burden by not demanding dozens of rounds to be decoded for each gate. However, they often require more complex correlated decoding across time – meaning the decoder might need to consider syndrome data over an entire algorithm’s runtime, not just instantaneously. This blurs the line between real-time decoding and post-processing, and is an active area of research.

For our purposes, the key point is that any novel QEC method still needs a powerful decoding algorithm, and the more data it has to crunch (either in parallel or accumulated), the more we need advanced classical processing.

Logical Operation Branching

As noted, the decoder must sometimes provide answers for conditional operations (e.g., was this logical qubit |1\rangle or |0\rangle after error correction?). In terms of system design, this means the decoder output must be fed back with low latency into the quantum control system. Many quantum control architectures now include FPGA-based real-time feedback channels for exactly this reason. For example, Rigetti’s control system was designed with a low-latency path from measurement results -> FPGA -> qubit drive, enabling feedback within a few microseconds. Integrating a decoder into that path is non-trivial; it’s effectively like inserting a tiny supercomputer into the feedback loop. The impressive Rigetti/Riverlane experiment showed it’s possible to do this and still keep latency under 10 µs for a conditional branch. As the complexity of algorithms grows (imagine many logical qubits doing branches in a complex sequence), coordinating multiple decoder outputs and ensuring none of them become a slowdown point will be a challenge. This is where architectural decisions – such as placing decoders hierarchically or having certain operations restricted to certain regions – might come into play.

Qubit Connectivity & Routing Efficiency

The physical topology of the quantum processor – which qubits can directly interact and how quantum information is shuttled between distant qubits – also impacts decoder performance.

Error-correcting codes like the surface code are designed for local, nearest-neighbor connectivity, which simplifies decoding by keeping error propagation confined. More advanced codes (e.g. certain quantum LDPC codes with higher rates) demand a richer connectivity graph to implement long-range stabilizers. If the hardware provides such long-range links or modular connections, it can reduce overhead by enabling those high-rate codes, but it also introduces new decoding challenges: errors can spread non-locally across the device, requiring the decoder to track and correlate distant syndrome data. In a distributed or modular quantum computer, the decoder may need to gather and process syndrome bits from multiple modules via entanglement links.

If routing qubits or performing teleported operations across modules adds latency or complex error correlations, the decoder must keep up – otherwise the benefits of increased connectivity are lost. Thus, qubit connectivity and routing efficiency (Capability B.4) are part of the co-design problem: the QEC protocol, decoder algorithm, and hardware architecture must be engineered together so that error correction remains effective at scale, no matter how the qubits are connected.

In short, decoder performance connects to everything: the quantum chip design (including its qubit connectivity topology), the measurement apparatus, the classical compute technology, and the overall fault-tolerance protocol. It’s a prime example of how building a quantum computer is a co-design problem between quantum and classical engineering. The good news is that progress in classical computing (FPGAs, ASICs, algorithms) can be relatively fast, piggybacking on decades of Moore’s Law advances – and we’re now applying that progress to quantum error correction.

Outlook and How to Track Progress

The trajectory for decoder performance is very promising, but significant work remains to go from today’s prototypes to the full-scale systems needed for CRQC. Here are some expected developments in the coming years and ways an interested reader or professional can monitor progress in this area:

Scaling up demonstrations

We can expect to see experiments demonstrating larger logical qubits and more concurrent logical qubits being actively error-corrected with real-time decoding. For example, a near-term milestone might be a full distance-5 or distance-7 surface code (requiring on the order of 50-100 physical qubits) running with a hardware decoder in the loop. This would show that not only can we decode quickly, but we maintain the error suppression benefits at a larger code size.

Keep an eye on announcements from major labs (Google, IBM, Amazon Braket’s QEC team, university consortia) for phrases like “real-time decoding”, “feedback error correction”, or “logical qubit demonstrations”. When Google’s 2023 result came out, it was widely covered because it crossed the “error correction threshold”. The next step is crossing that threshold with integrated decoders – something we’ll likely hear about as soon as it’s achieved.

Improvements in decoder hardware

The record-setting ASIC decoders show that bespoke silicon can provide incredible performance. In the coming years, we’ll likely see more ASIC implementations of different decoder algorithms, perhaps integrated as part of a quantum control chip. For instance, if a company like IBM or Intel creates a control chip for their quantum processor, they may include on-chip decoding accelerators.

Watch for research papers or presentations on “cryogenic decoders” or “ASIC decoders for QEC” – the Nature Electronics paper by the Riverlane team is one example, and it’s reasonable to anticipate follow-ups that handle even larger codes or integrate more functionality (like decoding and feeding forward signals in one package). Conferences on quantum computing and classical hardware (e.g., APS March Meeting, IEEE Quantum, or Supercomputing conferences) often have talks on these hybrid systems.

Software and algorithm advances

On the algorithmic front, even small boosts in decoding efficiency or accuracy can be valuable. One area to watch is machine learning/deep learning decoders, which some research suggests could adapt to noise and potentially be implemented on neuromorphic hardware for speed. If those show promise, they could become candidates for hardware implementation.

Another area is decoders for biased noise or specific error models – for example, systems where one type of error (say Z errors) is more common than others can use tailored decoders to raise thresholds significantly (there have been examples of error rates tolerating >10% for certain biased-noise decoders).

Progress in these specialized decoders will be reported in quantum computing journals and the arXiv; the Error Correction Zoo (an online knowledge base) is also a great resource for tracking different decoder types and their theoretical performance.

Integration into full quantum stacks

Ultimately, a decoder won’t live in isolation – it will be part of a full quantum computing stack including control electronics and software. Companies like Quantum Machines, which build quantum control hardware, publish updates on how their systems can support fast feedback and decoding. Riverlane’s product Deltaflow is specifically aimed at real-time QEC integration.

Monitoring these companies and their roadmap announcements can provide insight into how close we are to seeing a turnkey decoder solution for large machines. When a major quantum hardware maker announces “we have a control system ready for 1000 qubits with real-time decoding,” that will be a significant readiness milestone.

Benchmarks and metrics

To gauge decoder progress, consider a few key metrics: latency per round, throughput (cycles per second), code size handled, power consumption, and logical error rate achieved. Over the next few years, we expect latency to stay on the order of sub-microsecond (as it’s already achieved in prototypes), but the code size handled will grow from the low hundreds into the thousands of qubits. Throughput should remain at or above the 1 MHz mark, even as scale grows – meaning solutions will emphasize parallelism. Power and area will become concerns when integrating multiple decoders; keep an eye on metrics like “milliwatts per qubit decoded” or similar. If an architecture can decode 1 million qubits with, say, 1000 ASICs at a few watts each, that might be acceptable in a data center setting (though challenging in a cryostat). These figures might emerge in academic papers or technical reports. The community may even develop standardized decoder benchmarks – for instance, decoding a standard dataset of syndrome bits from a certain code and noise level, and reporting throughput and accuracy. Any emergence of such benchmarks or competitions would be a sign of maturing technology.

Conclusion

In conclusion, decoder performance has evolved from a theoretical footnote (“assume fast classical processing”) into a vibrant sub-discipline at the intersection of quantum computing and classical hardware design. It is no exaggeration to say that without real-time decoders, there will be no large-scale quantum computers – the two must rise together. The progress in the last few years, from demonstrating below-threshold error correction to integrating sub-microsecond feedback loops to engineering chips decoding a thousand qubits in nanoseconds, shows that the field is meeting this challenge.

To reach CRQC, the focus now is on scaling and reliability – proving that these decoders can handle the torrent of data a million-qubit machine will produce, 24/7, without missing a beat. As you track quantum computing developments, watch for those decoder milestones; they are one of the clearest indicators of how close we are to the quantum era where cryptography and computing will be fundamentally transformed.

Technology Readiness Assessment (Nov 2025)

As of late 2025, Capability D.2 (Decoder Performance for real-time QEC) is in the advanced testing phase (TRL ~5). The concept of high-speed quantum error decoders has been proven viable: we now have specialized decoder algorithms and even prototype hardware (FPGAs/ASICs) that can handle error-correction for small codes in real time. For example, recent demonstrations showed decoder chips processing syndrome data for on the order of 1000 physical qubits with sub-microsecond latency, all within power and size constraints suitable for cryogenic integration. This is a huge validation that decoding can keep up with quantum hardware at least at “patch” scale.

The remaining gap is one of scaling: going from handling, say, a few dozen logical qubits for a few seconds to handling hundreds of thousands of physical qubits continuously for days. In practical terms, decoders need to be networked and made fault-tolerant themselves to deal with the deluge of syndrome data a CRQC will produce. The current TRL ~5 indicates that decoder technology is validated in a relevant environment (e.g. integrated with small quantum setups); to reach the next levels, we’ll look for milestones such as decoder systems managing real-time QEC on significantly larger arrays (hundreds or thousands of qubits) or running non-stop error correction for extended periods without failure.

Another key sign will be the deployment of hierarchical or distributed decoders – multiple decoding units working together to cover a full-scale device. Given that decoding is the “classical backbone” of a quantum computer’s error correction, its high readiness is encouraging for the overall roadmap. Continued progress in this area (e.g. improved algorithms, faster electronics, and successful long-duration decoder tests) will further solidify confidence that we can correct errors as fast as they occur, even in a million-qubit machine.

Quantum Upside & Quantum Risk - Handled

My company - Applied Quantum - helps governments, enterprises, and investors prepare for both the upside and the risk of quantum technologies. We deliver concise board and investor briefings; demystify quantum computing, sensing, and communications; craft national and corporate strategies to capture advantage; and turn plans into delivery. We help you mitigate the quantum risk by executing crypto‑inventory, crypto‑agility implementation, PQC migration, and broader defenses against the quantum threat. We run vendor due diligence, proof‑of‑value pilots, standards and policy alignment, workforce training, and procurement support, then oversee implementation across your organization. Contact me if you want help.