Silicon Spin Qubits Achieve >99% Fidelity in 300‑mm Foundry Fabrication

Table of Contents

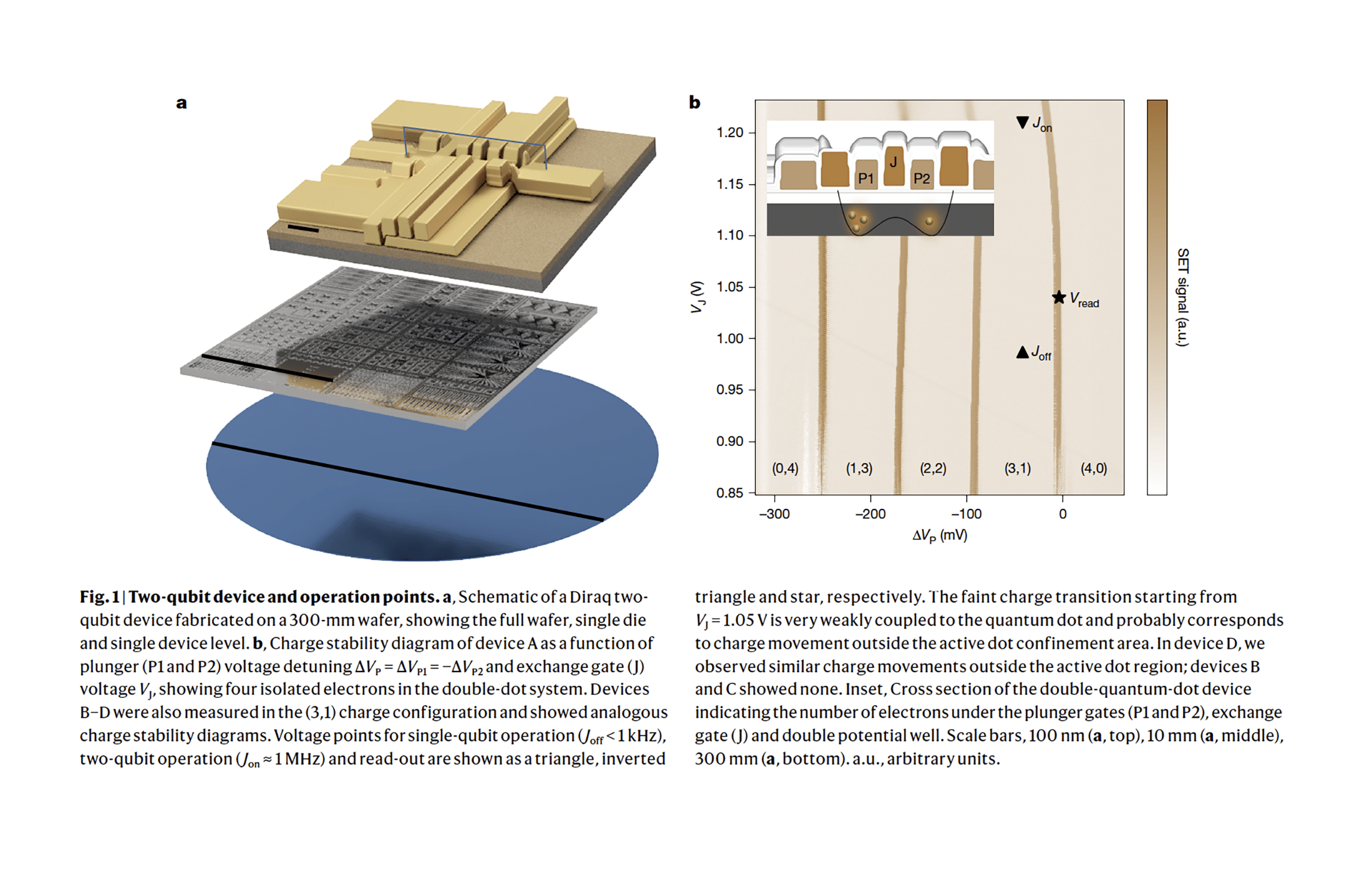

24 Sep 2025 – The race toward large-scale quantum computing just hit a significant milestone. In a new Nature paper “Industry‑compatible silicon spin‑qubit unit cells exceeding 99% fidelity” (open access) a team from Diraq and imec reported that they achieved better than 99% gate fidelity for silicon spin qubits manufactured using standard 300 mm semiconductor fabrication processes.

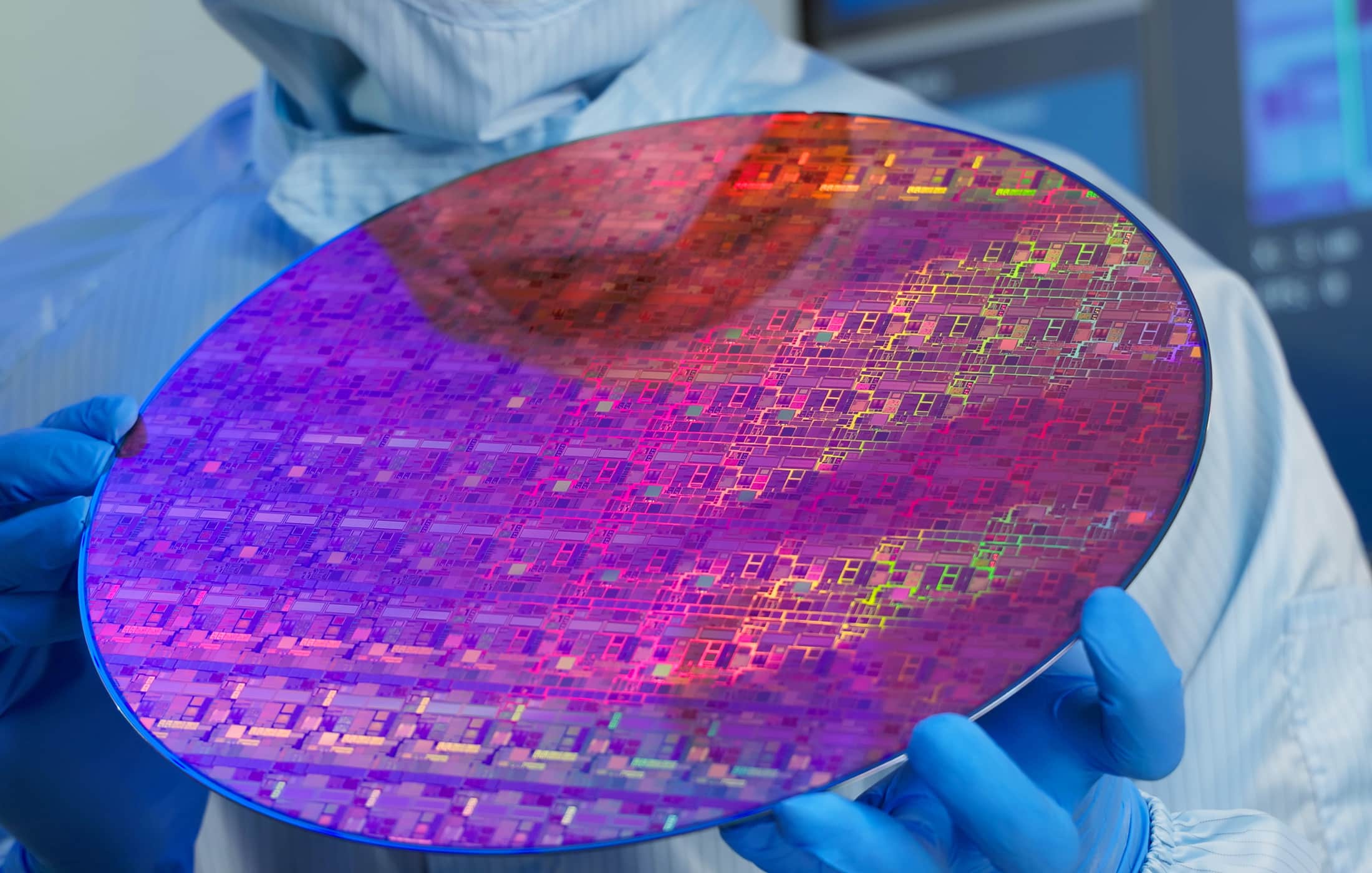

Crucially, this wasn’t a one-off demonstration: four separate two-qubit devices on the same silicon wafer all showed error rates below 1% for every fundamental operation, including single-qubit and two-qubit gates. Even state preparation and measurement (SPAM) were exceptionally reliable, with three devices exceeding 99.9% readout fidelity.

These results mark the first time silicon qubit “unit cells” built in an industry-compatible CMOS foundry have hit the kind of fidelity benchmarks long seen as necessary for fault-tolerant quantum computers.

Key Findings: 99%+ Fidelity Across All Operations

The paper highlights that both single-qubit rotations and two-qubit entangling gates surpassed the 99% fidelity threshold on every device tested. For example, in one device a controlled-Z (CZ) two-qubit gate achieved about 99.3-99.5% fidelity, while single-qubit X rotations were around 99.5% and z-axis rotations (implemented as virtual phase shifts) reached ~99.96%.

Initialization and read-out were even more precise, with combined SPAM fidelity above 99.9% in most units.

Equally important, the team demonstrated this performance reproducibly: all four silicon chip devices (labeled A through D) performed at comparably high fidelities. Such consistency across multiple qubits on a wafer indicates that the manufacturing process is well-controlled and repeatable – a key prerequisite for scaling up quantum processors.

These silicon spin qubits are essentially single electrons trapped in quantum dot potential wells, with the electron’s spin serving as the qubit state. The devices use a planar MOSFET-like geometry with polysilicon gates, deliberately hewing to a conventional CMOS process flow. Despite this industry-friendly architecture, the qubits displayed exceptional coherence properties. The devices were fabricated on an isotopically enriched silicon wafer with a very low concentration of residual nuclear spin-carrying isotopes (400 ppm ²⁹Si). In these devices, the researchers reported long spin relaxation times T₁ up to 9.5 seconds and Ramsey coherence times T₂* of 40.6 µs. By using Hahn echo pulse sequences to mitigate slow noise, the coherence time was extended dramatically, reaching 1.9 ms.

Achieving such long-lived, controllable qubits in an industry-standard silicon wafer process answers a longstanding question: Can high-performance qubits be made in a mass-production foundry? The answer, resoundingly, is yes.

CMOS Compatibility and Why It Matters

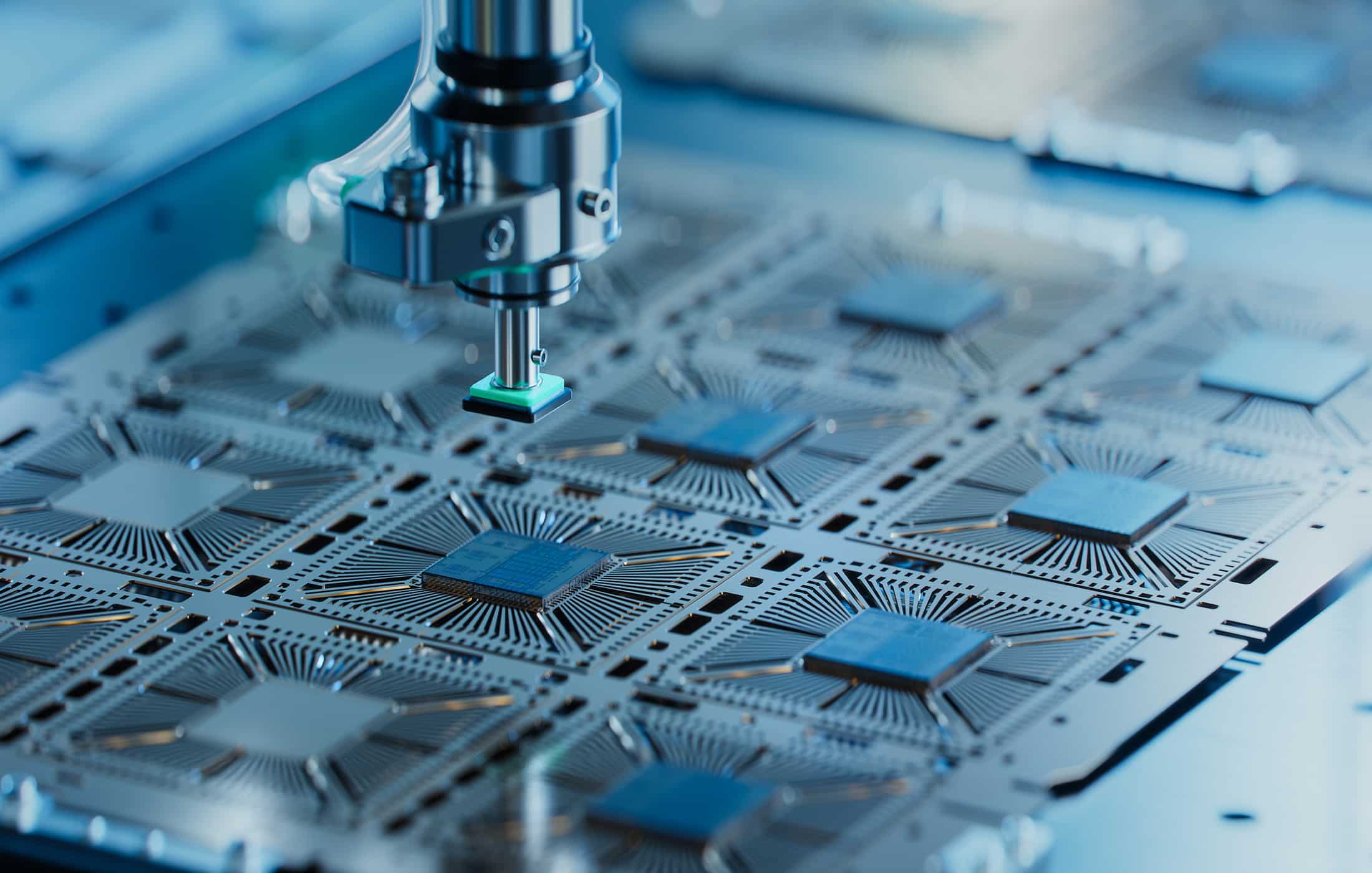

The significance of exceeding 99% fidelities using commercial CMOS-compatible processes cannot be overstated. Unlike exotic quantum hardware that requires specialized fabrication, these silicon spin qubits were made in imec’s 300 mm semiconductor foundry using materials and methods very close to conventional chip manufacturing. In fact, the qubit chip’s layout is a “planar MOS” double quantum dot adjacent to a silicon transistor sensor – a design that leverages decades of CMOS engineering.

By demonstrating that such a mainstream process can yield qubits with error rates at or below the commonly targeted 1% threshold, the study paves the way for leveraging the full might of the silicon industry. As the authors note, they are effectively reconciling traditional CMOS with qubit fabrication, so the field can “benefit from the installed capabilities for mass manufacturing at economical costs.”

In practical terms, this means quantum chips might be scaled up similar to classical microchips. Fabricating on 300 mm wafers allows hundreds or thousands of qubit devices per batch, with high uniformity. Such foundry-enabled scalability is critical for quantum computing’s future. “This proof point is a key milestone that paves the way towards integrating high-quality qubits with standard CMOS transistors on a single chip,” said Diraq CEO Andrew Dzurak. Diraq has already designed chips to be made in GlobalFoundries’ 22 nm CMOS line, aiming to monolithically integrate qubits and classical control logic. If successful, this approach could allow millions of qubits on one chip, since silicon spin qubits are extremely small – comparable in size to a normal transistor.

This stands in contrast to modalities like superconducting qubits or trapped ions, which currently require much larger device footprints and specialized fabrication. In short, achieving >99% fidelities in silicon qubits made by a standard fab means the quantum computing industry can ride on the back of existing semiconductor infrastructure – a faster and potentially cheaper road to scale.

Toward Scalable, Fault-Tolerant Quantum Computing

High gate fidelities matter because they bring us closer to the regime of fault-tolerant quantum computing, where errors can be corrected faster than they accumulate. Most quantum error-correcting codes require physical qubit error rates on the order of 10⁻³ to 10⁻² (0.1-1%) to function effectively. The >99% (i.e. <1% error) process fidelities achieved by the Diraq/imec devices are at this crucial threshold. In fact, the team specifically notes that their one- and two-qubit gate errors are “approaching and surpassing the fault-tolerance threshold for the widely studied surface code.” For the surface code (a popular error-correction scheme), a typical fault-tolerance threshold is around 1% error per gate; the reported 0.5-1% error rates are essentially there. This implies that a large array of such silicon qubits, if they can be controlled in parallel, would in principle be capable of running error-corrected quantum algorithms.

Equally importantly, these fidelities were obtained while scaling up to multiple qubits in a realistic environment. Until now, many record-breaking qubit experiments were done on individually optimized devices in academic labs. By showing uniform high performance across several foundry-fabricated devices, the Nature paper validates that one can maintain qubit quality at scale. This builds confidence that adding more qubits (tens, hundreds, eventually thousands) won’t introduce unpredictable error bursts or yield loss that derail a large quantum processor.

In other words, the results suggest silicon spin qubits have a viable “scaling pathway towards commercially viable quantum computing with potentially millions of qubits on a single chip.” The demonstration thus intensifies the race toward a scalable, fault-tolerant quantum computer: it shows that one of the most silicon-friendly qubit technologies is keeping pace with the performance needed for error correction, while inherently offering a path to massive integration.

Isotopic Purification: Quelling Decoherence at the Source

One intriguing aspect of the Diraq/imec study is why these qubits performed so well – and what the remaining error sources are. The researchers performed detailed error characterization using gate set tomography (GST), which revealed that the dominant infidelity in their devices comes from nuclear spin noise in the silicon lattice. Natural silicon contains about 4.7% of the isotope $$^{29}$$Si, whose nuclei have a spin of 1/2. These nuclear spins create fluctuating magnetic fields that can randomly perturb the electron spin qubits (causing what the team describes as “slow jumps” in qubit Larmor frequency). In the reported devices, those sporadic nuclear flips – not imperfections in the fabricated structures or control electronics – are the primary limit on fidelity.

This is actually good news. It means the qubit errors are stemming from a known, addressable cause: materials decoherence, rather than some unremoveable technological flaw. As the authors note, the residual nuclear-spin noise can be “solved with further isotopic purification” of the silicon. And authors explain how they might approach it as their next target. By eliminating that hurdle with isotopically purified silicon, silicon spin qubits could soon rival the absolute best gate fidelities of any platform – while still being made in conventional fabs.

Implications for Q-Day and Quantum Security

Beyond the hardware headlines, achievements like this have ripple effects for quantum security threat modeling. “Q-Day” is the notional day when a quantum computer becomes capable of breaking present-day cryptography – effectively the day a cryptographically relevant quantum computer (CRQC) comes online.

While estimates for Q-Day vary, many experts warn it could arrive by the early 2030s or even sooner. Results such as Diraq’s high-fidelity foundry qubits lend weight to those sooner-than-expected timelines. The reasoning is straightforward: to threaten classical encryption (for example, by running Shor’s algorithm on RSA-2048), a quantum computer will likely need millions of physical qubits with error correction. That sounds daunting, but if those qubits can be manufactured using existing CMOS technology – as this work demonstrates – the engineering challenge looks far more tractable.

Every technical hurdle overcome (scalable fabrication, >99% gate fidelity, long coherence, etc.) accelerates the march toward a large-scale quantum machine capable of cracking RSA/ECC cryptosystems. In short, the timeline to Q-Day is contracting, as milestone after milestone is achieved in quantum labs and now in foundries.

The broader implication of this paper is that quantum computing is steadily graduating from lab experiments to an engineering discipline. Just as the invention of the integrated circuit paved the way for today’s computing revolution, the ability to fabricate quantum dot qubits in a foundry foreshadows a future quantum IC.

Quantum Upside & Quantum Risk - Handled

My company - Applied Quantum - helps governments, enterprises, and investors prepare for both the upside and the risk of quantum technologies. We deliver concise board and investor briefings; demystify quantum computing, sensing, and communications; craft national and corporate strategies to capture advantage; and turn plans into delivery. We help you mitigate the quantum risk by executing crypto‑inventory, crypto‑agility implementation, PQC migration, and broader defenses against the quantum threat. We run vendor due diligence, proof‑of‑value pilots, standards and policy alignment, workforce training, and procurement support, then oversee implementation across your organization. Contact me if you want help.